十年内存终升级,DDR5 商用驶入快车道

内存的新时代要来了。

从最早的作为焊接在主板上的 IC 电子元件,到更为人性化的“插拔式”内存条,内存条的发展也经历了从 SIMM(单列直插式内存模块)、EDO DRAM(扩展数据输出内存)、SDRAM(同步动态随机存取内存)到 DDR(双倍速率同步动态随机存储器)这几个阶段的技术革新,DDR 作为一种在性能与成本之间折中的解决方案,从一出生就占据着明显优势,并经历了 DDR2、DDR3、DDR4 的更迭,但与此同时也迎来了新的问题。

从本质上讲,内存分为作为程序运行的空间(DRAM)和存储数据的空间(NAND)两个用途,但在现阶段,单位价格的增长容量缓慢和速度跟不上 CPU、由于在每个时钟周期内要给小电容重新放电造成的能耗过高的问题,成为了商业用户的心头之痛,无论是数据中心、高性能计算还是运营商网络,DRAM 的这些问题都带来了不小的麻烦。DRAM 的技术瓶颈无法满足日益增长的容量速度功耗需求。

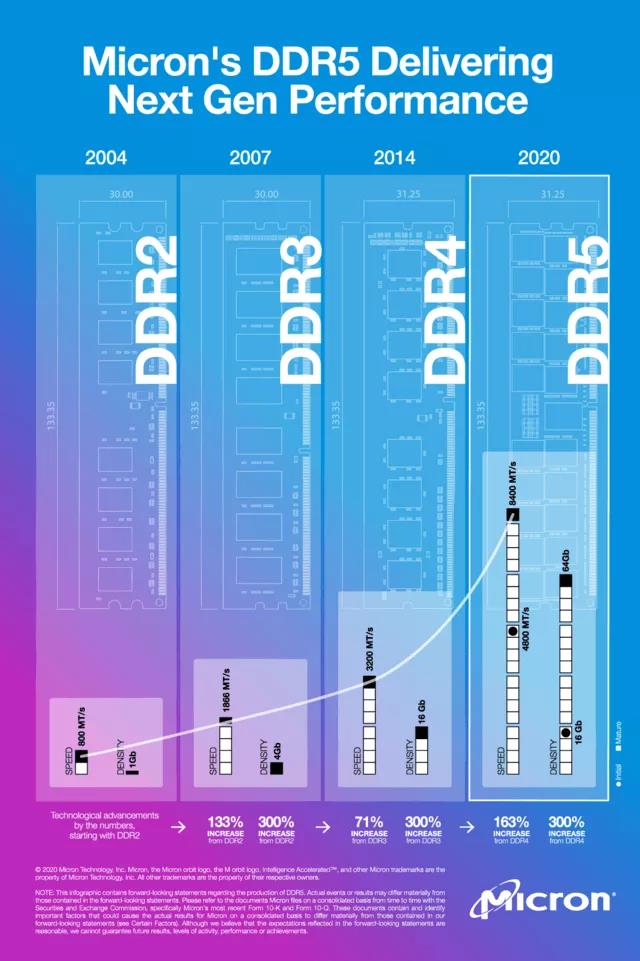

DDR 图示

基于 DRAM 本身的局限性,DDR 的进步也比较缓慢,从 DDR3 到 DDR4 的进步足足花了 5 年有余,而市面上“最新”的 DDR4,也是在 2012 年开始发布第一版的。得益于半导体工艺的进步,在今年 7 月份,JEDEC 固态技术协会也是发布了下一个主流存储器标准 DDR5 SDRAM 的最终规范,这可谓是千呼万唤始出来,同时也标志着存储器开发的又一个重要里程碑。

JEDEC 发布 DDR5 规范

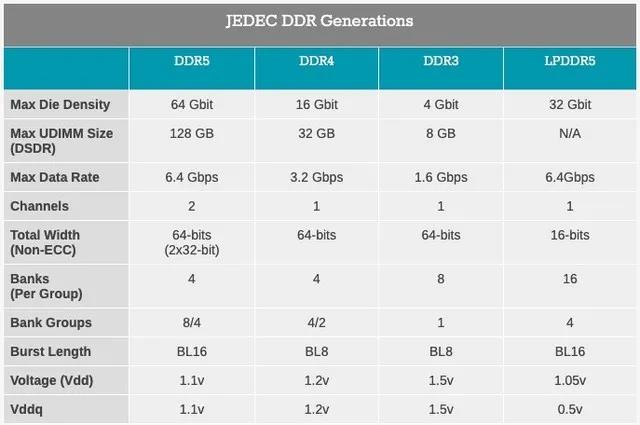

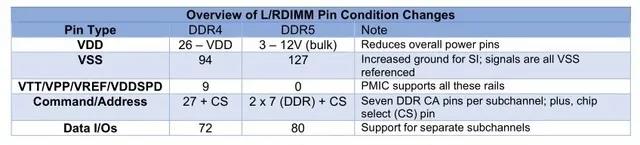

虽然按照 JEDEC 原本的计划,DDR5 的最终规范本应该在前年推出,但丝毫没有影响 DDR5 最终规范的重要性,与之前的每次迭代更新一样,DDR5 的内存密度和速度再次得到了更新。单个存储芯片达到了 64Gbit 的密度,相较 DDR4 的最大 16Gbit 密度提升了 3 倍;最大内存速度为 6.4Gbps,是 DDR4 的两倍;Burst Length 从 8n 增加到 16n 这样在时钟频率不变的情况下可以实现带宽翻倍。

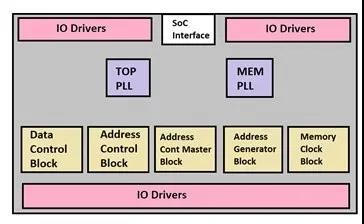

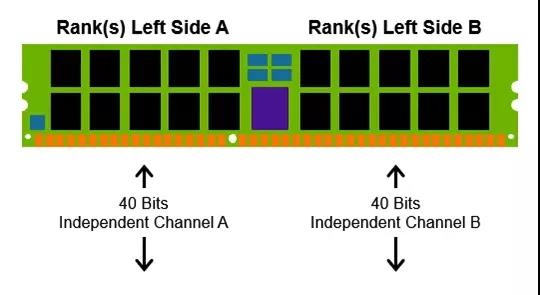

DDR5 可以使系统通道数再翻倍

与此同时,DDR5 也有一些新特性,例如 I/O 和 CA 通道的训练模式、DFE、On-die ECC 等功能,都是对服务器、数据中心等等的重大利好,但这些这也将带来更多的设计、测试和兼容挑战。预计到 2023 年上半年,DDR5 将成为主流的 DRAM 技术,基于新标准的硬件将在服务器级别开始采用,然后再推广到客户端 PC 和其他设备。美光首席架构师、高级技术成员、JEDEC 理事会成员 Frank Ross 表示,DDR5 标准为业界提供了主存性能方面的关键进步,使下一代计算能够将数据转化为对云、企业、网络、高性能计算和人工智能应用的洞察力。

而上文曾提到的能耗过高的问题也有望在 DDR5 时代得到解决,DDR5 的 Vdd 从 DDR4 的 1.2V 降低到了 1.1V,性能得到了翻倍,从而降低了每bit的功耗。IT 行业不断增长的能源需求是一个日益严重的问题。之前曾有数据预测到 2030 年,IT 技术和通信技术将消耗全 20% 的电力,而这会随着人工智能、区块链和大数据等高性能应用消耗越来越多的能量而不断增加。例如,训练一个人工智能模型,其碳排放量是美国普通汽车平均寿命期内(包括制造过程)排放的 5 倍。对于那些注重气候和预算的企业来说,DDR5 不仅可以节省数据中心的运营成本,同时也让他们无需担心能耗过高的问题。

相比 DDR4,DDR5 的 VDD 降低到了 1.1V

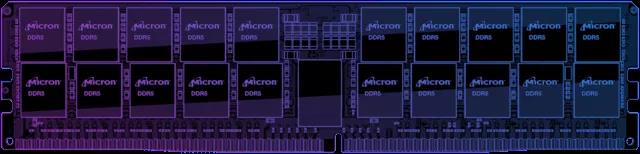

作为一家创新内存和存储解决方案的厂商,美光在今年 1 月份宣布将开始出货 DDR5 寄存型 DIMM(RDIMM),以第三代的 10 纳米级 1z 纳米制程打造(1z 纳米制程大概位于 12 到 14nm 节点之间),ECC DIMM 规格,频率 DDR5-4800,相较 DDR4-3200 存储器性能提升了 87%,从而应对下一代服务器负载。

如同以往一样,每次制定新的 DRAM 标准时,必须要克服很多挑战才能开发出性能过硬的解决方案,美光从一组与性能、功耗和特性相关的目标开始入手,将每个目标与其他目标进行对比分析,以找到架构的“最佳应用点”。同样地,在设计复杂性、功耗和性能方面,美光的设计和验证团队、架构专家和产品工程团队在 DDR5 的定义和开发过程中,通过加强协作来设计电路和系统,并进行全面的仿真和数据分析,最终得到了相对完善的设计。

为了实现较高的目标宽带,美光结合了 DFE 等新特性,目的是使系统能够在所要求的信号和时序余量下工作。为了提高可靠性并支持将来的 DRAM 扩展,美光在设计过程中增加了硅片纠错码,从而可以对很多不同的方案进行评估以促进最优实现。而一些其他从 DDR4 升级到 DDR5 的新特性,例如使用单周期对比双周期命令,以及增加命令总线带宽等,则需要在功耗和复杂性之间进行权衡,最终采用了新的刷新模式来提高数据总线的利用率,但增加了复杂性。

美光年初出货 DDR5 寄存型 DIMM

当前快速扩展的数据集和计算密集型应用程序导致的高级工作负载促进了处理器内核数量的增长,而当前的 DRAM 技术难以满足其带宽需求。DDR5 对由指数级数据增长驱动的下一代应用,例如大数据、高性能计算、人工智能和机器学习应用十分有利。在 Frank Ross 看来,为了处理流经这些应用的大量数据,服务器和数据中心基础设施需要更大的内存带宽,而这是前几代 DRAM 做不到的。随着数据的爆炸式增长,从这些数据中心工作负载中实现价值并提取价值的关键在于 DDR5 可以提供性能更高、密度更大、质量更好的内存。

DDR5 与前几代 DDR 内存性能对比

为了确保合作伙伴能够随时获得他们所需的技术信息和产品来消除采用 DDR5 时可能遇到的障碍,今年 7 月美光启动了一项综合的技术赋能计划(Technology Enablement Program, TEP),在该项计划中,之前采用 DDR4 的企业可以随时获得过渡到 DDR5 时所需要的的资源。随着商用 DDR5 支持平台的推出,美光也将提供 DDR5 颗粒和模组的指南,从而帮助企业根据实际需求选择和验证合适的美光 DDR5 产品。

美光启动 DDR5 赋能计划

加入到赋能计划的合作伙伴,除了可以得到美光提供的物理样片之外,还可以得到电气和热模型、行为/功能模型、信号完整性模型和生态系统支持。从而提升服务器平台和嵌入式系统的开发。

美光计算与网络事业部业务发展总监 Jim Jardine 称:“在 DDR5 生命周期的这一阶段,我们不仅重视为合作伙伴提供美光产品相关的信息和资源,更重视在合作伙伴与生态系统之间建立联系,这些生态系统的合作伙伴可以帮助设计 DDR5 接口和控制器,例如 Cadence、Montage、Rambus、Renesas 和Synopsys 等企业。”

与任何新生技术一样,DDR5 整个的生态系统也需要时间并整合产品和解决方案。美光方面认为其专长、知识和带头作用有助于指导合作伙伴采用 DDR5。其 TEP 计划和全球布局规模使得合作伙伴更容易参与其中。美光的赋能计划旨在为这些合作伙伴提供一种智能的方式来实现自助服务,例如方便的获取电气和热模型、数据手册和培训材料,以便他们能够以适合自己的速度向前推进。

作为 DDR4 的后继者,DDR5 是下一代同步动态随机存取存储器。从 DDR4 到 DDR5 的跨越是一个更大的飞跃,在需要更多带宽的驱动下,DDR5 性能更强、可扩展性更高、支持密度更高,在引领大数据和 AI 时代方面,牢固地占据了一席之地。美光作为较早做出 DDR5 规划的厂商,不仅早早将 DDR5 纳入路线图,并在今年推出了 1z 纳米制程 DDR5 寄存型 DIMM ,并计划在未来陆续推出 1α 和 1β 纳米制程。在可预见的未来数年来,无论是技术还是产品方面,DDR5 的成熟终将为存储市场再次注入新的生命力。

声明:本文出自公众号【美光科技】,原文出自中关村在线,转载目的在于信息传递,版权归原作者所有,如涉及侵权,请联系删除。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:1857次2019-11-14 14:55:24

-

浏览量:4743次2021-04-23 17:06:31

-

浏览量:1719次2023-02-02 10:55:28

-

浏览量:2263次2018-07-26 10:16:39

-

浏览量:2604次2022-03-06 09:00:12

-

浏览量:707次2025-11-19 14:55:52

-

浏览量:2725次2018-01-02 16:10:27

-

浏览量:3443次2020-11-24 16:13:16

-

浏览量:1370次2024-01-05 13:52:07

-

浏览量:1549次2023-03-23 18:35:11

-

浏览量:2999次2020-11-11 09:42:43

-

浏览量:2674次2020-07-09 19:00:01

-

浏览量:5731次2021-01-12 09:39:20

-

浏览量:4060次2020-11-03 10:31:30

-

浏览量:3567次2019-11-18 14:16:23

-

浏览量:2282次2018-07-22 12:15:28

-

浏览量:1865次2019-12-20 09:28:00

-

浏览量:2509次2018-02-27 19:56:01

-

浏览量:2742次2018-06-18 11:34:13

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

易百纳技术社区

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友