干货分享 | 如何高效预测 ESD 放电电流?(下)

本文运用 SEED 方法对开放技术联盟 [1] 提出的“ESD 放电电流测量”指标建模并将结果与实测值进行了比较。同时讨论 SEED 模型模块(见图1)的特性和实现方式。特别讨论了共模扼流圈和外部 ESD 保护器件的建模问题,因为二者是非常重要的因素,决定着整个系统的系统级 ESD 稳健性。运用 TLP 和 ESD 发生器模型评估了 ESD 脉冲上的瞬时系统级响应和进入 IC 的残余电流。

由于文章较长,我们将文章分成三次发布,您现在看到的是(下)篇,也是最后一篇。

外部 ESD 保护器件的特性表征与建模

根据 [1] 提出的规范,外部 ESD 保护器件位于系统板连接器附近。在这个位置上,可以在一定程度上保障整个系统的稳健性,不仅保护 IC ,同时还能保护信号路径中的所有分立式元件(如电容和 CMC)。为了预测系统行为以及系统在不同 ESD 水平下的稳健性,我们需要一个精确的外部 ESD 保护模型。这里使用的是一个硅基 ESD 保护2器件,其触发电压 Vt = 120 V,回弹电压 Vh = 32 V,动态电阻Rdyn = 0.1 Ω。

在此实现方案中,我们对所选 ESD 保护器件的静态和动态行为进行了建模。为此我们使用了一种基于 [6] 所述方法的改进型动态模型。

借助电压控制开关和二极管SPICE模型对 ESD 保护器件的静态行为建模,该静态行为包括泄漏区、回弹(导通)区、线性区和非线性(热不稳定)区域。在 ESD 脉冲的第二个峰值期间,RC 网络和反馈环路负责开关状态。模型的动态行为是通过两个 RC 集成网络实现的,这些网络以特别方式组合起来,以便控制 ESD 保护器件上的压降及其在施加的 ESD 脉冲的第一个峰值期间的衰减时间。

扩展动态模型的主要优点是可以正确表征 ESD 保护器件的热行为,并且可以更精确地描述电导率调制和感应过冲的影响。在本文中,电导率调制效应对发生于外部保护端的电压过冲的表征至关重要,将以峰值电流的形式通过 CMC 传递至 ICI/O引脚。

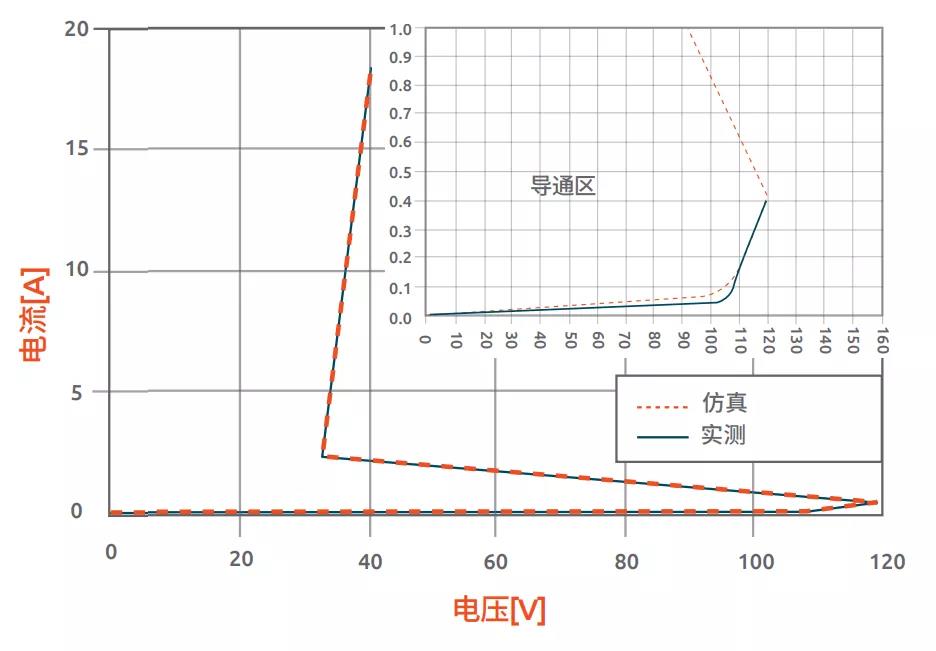

依照 [6] 所述程序,将改进的动态模型拟合到 TLP 实测数据,结果如图9所示。

图9:外部硅基 ESD 保护器件的实测和仿真图,电压和电流在 70 ns 至 90 ns 之间取均值。

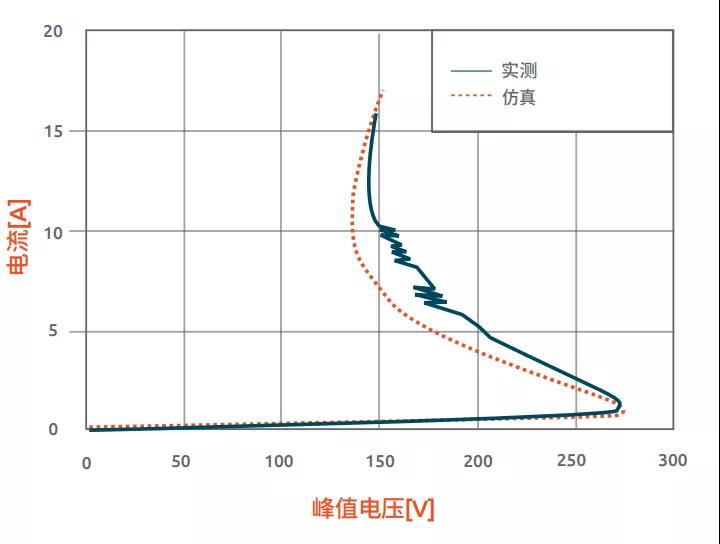

为了评估 ESD 器件的动态特性,如电导率调制和感应过冲,必须特别注意在施加的 ESD 脉冲的最初几纳秒内出现的电压和电流峰值。图10所示为峰值电压与 TLP 电流的关系。在图中可以观察到强大的电导率调制效应。改进后的动态模型很好地捕捉了这种效应。

图10:外部硅基 ESD 保护器件的实测和仿真图,采用1ns上升时间 TLP 脉冲的峰值电压和电流。

系统模型验证

在介绍了 SEED 模型的各个组成部分之后,我们依据带和不带外部 ESD 保护器件的参考板的实测值,使用 TLP 对整个系统模型进行了验证(见图1)。

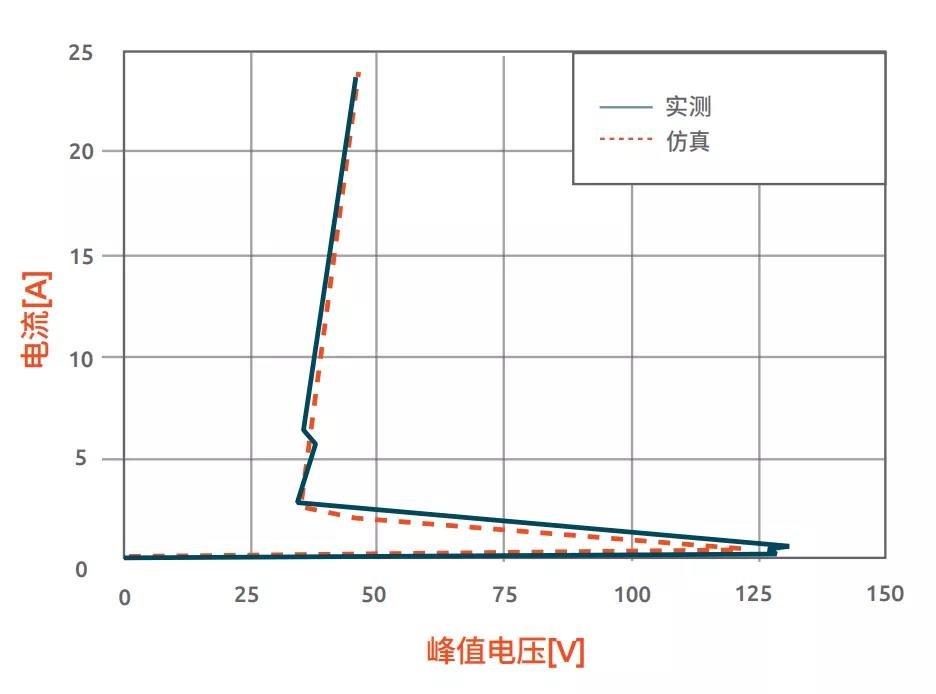

无外部 ESD 保护的参考板

图11显示了参考系统的 TLP 测量结果(见图2,包括 CMT 、去耦电容、 CMC 和 IC 网络,不包括外部 ESD 保护器件),并将它们与使用所述 SEED 模型所有对应组件获得的仿真结果进行了比较。这里未使用 ESD 发生器模型和外部 ESD 保护模型。对 TLP 脉冲建模时使用的是理想脉冲源和 200 ps 上升时间滤波器,从而使目标系统捕获脉冲上的模拟脉冲波形在100V TLP 下得到优化。仿真程序对测量值进行重度重采样。

图11:未保护参考电路板的实测和仿真图,电压和电流在 100ns TLP 脉冲的 70 ns 到 90 ns 之间取均值。

带 ESD 外部 ESD 保护的参考板

图12所示为带有外部 ESD 保护的参考板的 TLP 图及其与使用 SEED 取得的仿真结果的比较情况。仿真程序高度再现了测量数据。

图12:带外部 ESD 保护器件的参考板的实测和仿真图,电压和电流在100ns TLP 脉冲的70 ns 到 90 ns 之间取均值。

根据结果,我们可以得出结论,所实现的 SEED 模型完全适合整体系统级稳健性的定性和定量预测。另外,该模型还可以用于采用不同系统模块和组件的初步测试。因此,在下一节中,我们将使用 ESD 枪模型测试该系统模型,从而对流入 IC 的瞬时残余电流进行评估。

应用

在实际环境中,人触摸系统板连接器的 GND 或I/O引脚时可能会发生 ESD 事件。在这种情况下,IEC61000-4-2 ESD 脉冲 [9] 将被注入系统并产生瞬时电流,结果可能会损坏系统 IC 。因此,我们将使用 ESD 发生器模型,以证明所提议的 SEED 模型(针对该模型的讨论和验证见第三节)是否具备复现借助 ESD 发生器模拟的真实 ESD 场景的能力。

图13和图14所示为 ESD 枪4 kV正放电的结果。在这种情况下,我们在 SEED 模型中使用了 ESD 发生器模型和外部 ESD 保护模型。

图13:带外部 ESD 保护器件的参考板的实测和模拟图动态过冲区放大图(ESD 枪放电 + 4 kV)。

图14:带外部 ESD 保护器件的参考板的实测和模拟图(ESD 枪放电 + 4 kV)。

两图均展示时域中得到的仿真电流曲线,同时显示了在 IC I/O引脚处测得的电流。黄红两色虚线分别展示了I级和II级 JEDEC HBM 标准 [2] 的限制。所用 SEED 模型提供了对测试系统的估算结果,预测值约比最大电流峰值高 20 %。但是,对于曲线的静态部分,仿真则会低估测量值。尽管存在这些偏差,但结果显示,所提议的 SEED 模型适合对此测量设置建模。

可以通过电磁耦合效应来解释在仿真结果与实测结果之间观察到的偏差,因为在实际 SEED 模型中不会遇到这些效应,即与 ESD 发生器继电器的串扰或电磁辐射相关的效应。在这种情况下,ESD 枪与测试板组件(如电路板走线、 CMT 网络或 CMC)之间的耦合效应可能对 ICI/O引脚上测得的最大电流造成破坏性的衰减。

为了尽量降低这些影响,可能需要额外做些工作,加强电路板对继电器直接冲击效应的屏蔽性能;在本例中,ESD 发生器尚未针对 DUT 进行屏蔽。同样,为了改善系统的建模行为,可以将 PCB 的 S 参数模型添加到 SEED 模型中。

结论

实践证明,在像 100BASE-T1 这样复杂的电路上运用 SEED 方法可以较好地估算系统在 ESD 条件下的整体瞬时响应;此类复杂电路包括使用复杂方法建模的各种组件,其目的是复现整个系统的静态行为,尤其是动态行为。此外,还可以运用该方法根据IEC61000-4-2 [9] 预测系统级 ESD 稳健性,根据JEDEC- HBM [2] 要求评估 IC 稳健性。

本文开发和验证的 SEED 模型可用于研究系统和外部 ESD 保护器件参数变化的影响,从而达到优化保护系统 IC 的目的,最大程度地减少工程设计和验证时间。

来源:安世半导体

- 分享

- 举报

暂无数据

暂无数据-

浏览量:5512次2020-10-22 10:55:15

-

浏览量:2605次2020-09-24 14:36:09

-

浏览量:2701次2019-01-24 17:11:51

-

浏览量:2937次2019-01-28 17:46:42

-

浏览量:1624次2019-10-17 17:10:12

-

浏览量:2571次2019-07-15 16:16:15

-

浏览量:2044次2020-06-05 11:53:54

-

浏览量:2732次2019-09-16 16:15:15

-

浏览量:2574次2020-06-30 18:37:38

-

浏览量:2141次2019-10-18 17:00:21

-

浏览量:5295次2019-09-09 16:52:23

-

浏览量:1931次2019-09-06 17:19:50

-

浏览量:2608次2020-06-22 14:12:56

-

浏览量:5046次2020-11-05 10:33:28

-

浏览量:2106次2019-08-01 15:42:00

-

浏览量:2204次2019-11-29 16:15:38

-

浏览量:3827次2019-11-21 09:11:36

-

浏览量:2746次2020-11-14 09:34:43

-

浏览量:5055次2019-01-26 17:32:14

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

易百纳技术社区

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友