SN65DPHY440SS Re-Timer驱动器意外跳变分析1

1. 前言

已经验证了部分工作在我的系统使用eval板。

现在把Re-Timer IC带到了自己的PCB上,配置相同,它不再工作了。

已经验证了数据和时钟正在通过Re-Timer并且输出结果与预期一致。

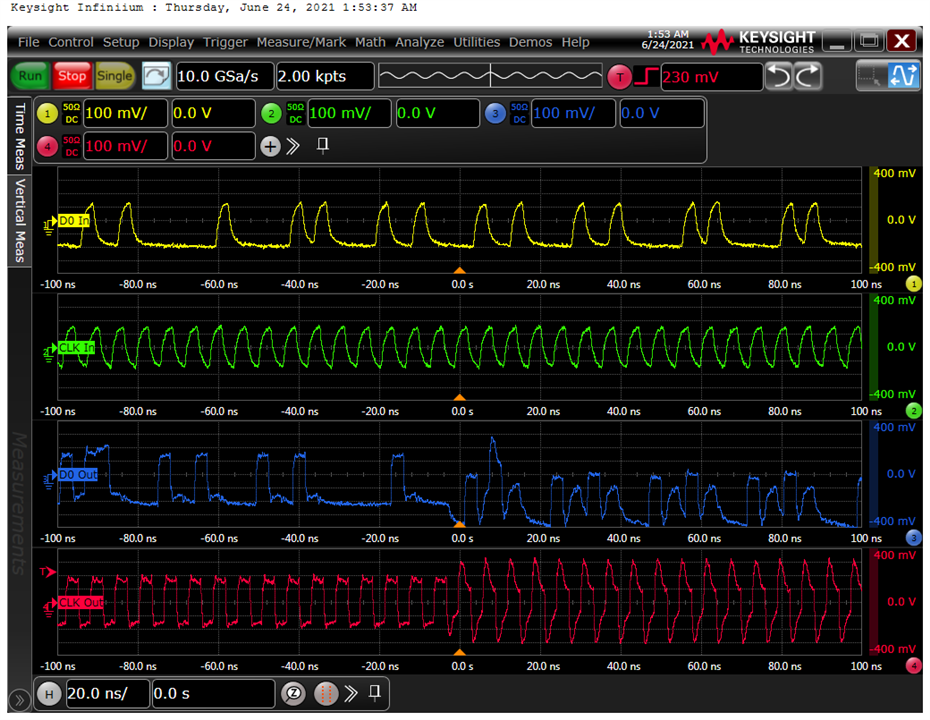

然而,我注意到的一件有趣的事情是,

输出驱动程序似乎会意外地(并周期性地)更改其驱动条件。

输入数据和时钟信号没有改变,但输出通过驱动器改变。

2 . 问题梳理

(1)MIPI-CSI还是MIPI-DSI设计?

MIPI-CSI

(2)MIPI-CSI应用程序,可以改用D0,切换到D1、D2或D3吗?

D0是电路的标签,但是它通过re-time的D3

(3)时钟是经过LP/HS还是始终停留在HS状态?

时钟总是处于HS状态,但数据在HS和LP之间传递

为了获取更多信息,我使用了2个数据通道,通过Re-Timer的D2和D3

其他数据输入被接地,其输出保持开放

3. 尝试使时钟保持高速状态

时钟总是在HS状态,

尝试将如下配置写到DPHY440寄存器总是使时钟在高速状态

(地址、数据)

(0x50, 0x10), // HS TX path Override enable

(0x51, 0x10), // HS TS path enable

(0x61, 0x00), // Disable LP path.

(0x70, 0x10), // HS RS path Override enable

(0x71, 0x10) // HS RX path enable按照上述配置更改了寄存器,得不到到输出

试过重置Re-Time,仍然没有输出任何东西

4. 确认eval板

(1)是否知道评估板(DPHY440SSRHREVM)是否配置为始终使时钟处于高速状态?

这个系统也适用于eval板。

除非通过其I2C寄存器进行配置,否则DPHY440将以其默认状态出现

期望是EVM上的DPHY440与主板上的DPHY440处于相同的状态。

(2)将DPHY440 EVM配置此设置中并验证EVM仍然工作?

我已经确认了DVM还能用。

(3)检查连接到DPHY440输出的设备是否试图进入LP状态?

我相当肯定连接到重新计时器输出的设备没有试图进入LP状态,

因为时钟总是停留在HS与DVM连接。

5. 检测原理图&上电时序

检查DPHY440的上电顺序

看看设计和EVM的上电顺序是否相同

除了VCC、VDD和Reset之外,还检查时钟和数据通道,

以确保它们都在LP11,直到DPHY440完成重置。

都正常

6. 信号捕获

下面是一个带有Reset、D0_N(单端)、VCC和CLK_P(单端)的捕获

Reset, D0_N(单端),VDD和CLK_P(单端)

- 分享

- 举报

暂无数据

暂无数据-

浏览量:4900次2021-07-03 16:35:19

-

浏览量:7164次2021-08-10 14:13:11

-

浏览量:2384次2023-11-23 15:09:34

-

浏览量:1153次2023-10-12 17:35:59

-

浏览量:5655次2021-08-10 14:24:09

-

浏览量:4575次2020-12-07 14:15:12

-

浏览量:7966次2020-12-08 09:48:56

-

浏览量:1471次2023-03-24 10:57:56

-

浏览量:1096次2023-11-01 17:33:57

-

浏览量:3838次2020-10-14 09:30:05

-

浏览量:9368次2020-11-26 14:22:19

-

浏览量:7937次2020-08-15 17:22:26

-

浏览量:4930次2021-09-22 16:39:28

-

浏览量:2842次2020-10-15 10:52:46

-

浏览量:3532次2020-11-11 10:44:22

-

浏览量:2102次2020-06-15 19:10:09

-

浏览量:947次2025-06-16 17:14:39

-

浏览量:2321次2020-06-23 17:33:04

-

2022-09-16 15:24:48

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

free-jdx

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友