全志R328硬件设计指南

本文档主要介绍 R328 芯片在应用方案设计中的原理图和 PCB 设计要点和注意事项,指导客户进行方 案硬件设计,保证硬件设计质量.

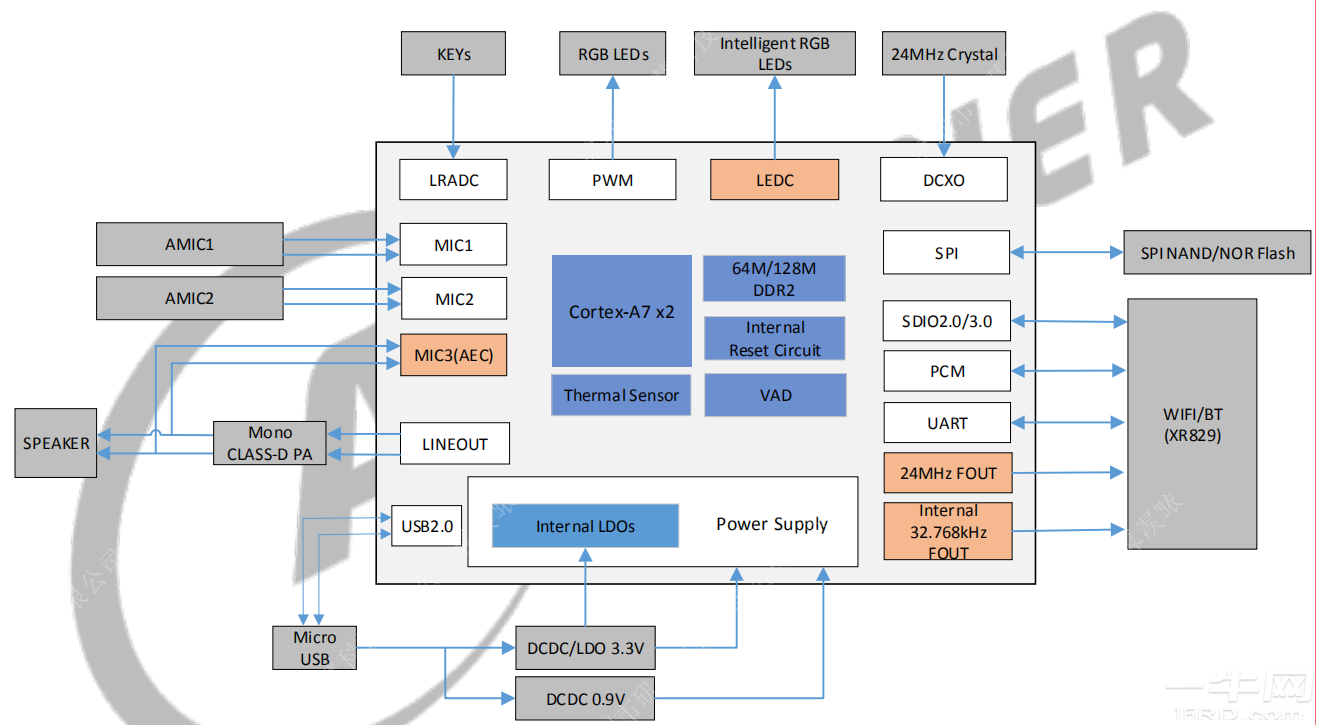

1.1.1. 系统硬件框图

R328 是一颗高集成度 SOC,主要应用于低成本智能音箱解决方案.集成双核 A7 处理器,频率可达 1.2GHz,为产品提供充足的运算能力;拥有丰富的音频接口 IIS/PCM,DMIC,OWA,MICIN,LINEOUT 以 及通用通讯接口 IIC,UART,SDIO,spi;内置 DDR,LDO,VAD,RESET,LEDC,24M/32.768K FOUT,简 化了系统方案设计,降低 BOM 成本.R328 系统硬件框如图所示.

1.1.2. 硬件系统基本工作原理

R328 硬件系统基本工作流程如下:

硬件系统正常上电,主控复位之后,CPU 开始执行 Brom 固化代码,对系统资源和关键外设进行 配置及初始化,包括电源,时钟,总线,复位,存储接口等.

根据配置,在 BROM 阶段将系统初始化信息(串口,DRAM 等)从存储介质读取到系 统 SRAM,进行芯片及系统的进一步详细配置和初始化工作;执行完 Boot0程序后进入 U-boot 阶段.

从外部存储介质中读取下一阶段需要的软件代码,启动操作系统,并对系统资源和外设进行管理.

操作系统启动之后,根据产品不同需求加载相关启动,比如 USB,音频,wifi,显示,蓝牙 等模块,最终完成开机启动,进入普通操作界面.

系统支持 watchdog 应用监视系统的运行,当程序跑飞或者发生死循环时,watchdog 模块会发出一 个复位信号,使 CPU 复位,软件系统重新启动. R328 硬件系统组成说明如表所示.

1.2. CPU 小系统

R328 CPU 小系统包括时钟系统,系统配置 PIN 和 DEBUG 部分组成.

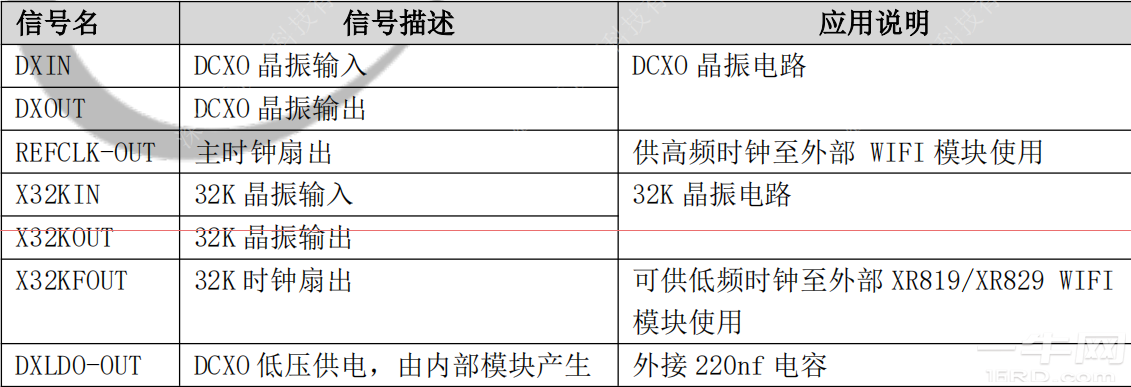

1.2.1. 时钟系统信号 PIN 说明

R328 硬件系统包含 DCXO/32K 两个时钟,对应时钟信号说明如表所示.

1.2.3. 主晶振电路

R328 DCXO 模块只支持 24M 主时钟.

DCXO 时钟模块可以通过 REFCLK-OUT PIN 扇出与主时钟同频率的 CLK 信号给 WiFi 模组使用,使用 24M Fanout 请联系 FAE 确认使用环境.

晶振选型参考如下:

当需要 DCXO 扇出时钟给 WIFI 使用时,晶振选型频偏≤10ppm;

当不需要 DCXO 扇出时钟给使用时,晶振选型频偏≤20ppm.

外挂匹配电容大小根据晶振规格和 PCB 而定,要求匹配电容+板级杂散电容总值等于晶振规格要求 的负载电容大小.

串接电阻需要预留位置,便于调试振荡幅度. 主时钟电路推荐参考设计如图所示.

1.3. 电源系统设计

1.3.1. SOC 端电源电容设计

R328 SOC 端各电源建议容值如下:

R328 CPU 可以采用独立电源域供电,支持动态调频调压功能,CPU 要有一个 10uF 以上的电容;

CPU 和 SYS 可以合并电源域供电,因 SYS 不支持动态调压,所以此时 CPU 不可以进行动态调压.

VCC-IO/VCC-PC/VCC-PE/VCC-PG/VCC-PLL/VCC-EFUSE 电源外挂 100nF 电容,靠引脚放置.

VCC-DRAM 电源需要有一个 10uF 电容以上,靠引脚放置.

AVCC 电容参照音频电路设计章节. CPU,SYS 和 DRAM 电源推荐电容组合如图所示.

微信扫码分享

微信扫码分享 QQ好友

QQ好友

暂无数据

暂无数据

我上传的资料

我上传的资料