FPGA逻辑设计回顾(9)DDR的前世今生以及演变过程中的技术差异

前言

本篇作为有关DDR的相关知识的第一篇,先给出DDR的前生SDRAM以及演变DDR/DDR2/DDR3等的总体概念与区别,后面会细分技术细节。文章参考互联网以及国外各大网站以及文献,水平有限,若有疏漏,还请谅解。

DDR的前世SDRAM

DDR的前身是SDRAM(Synchronous Dynamic Random Access Memory),即同步动态随机存取存储器。所谓的“同步”,就是我们平时说的同步数据的同步,要想同步,必须有时钟,也就是时序电路。存储器也有非同步的,例如:异步双端口RAM,就不需要时钟: Dual Port RAM Asynchronous Read/Write

它对数据的读写用RTL语言描述大概是这样的(部分代码):

// Memory Write Block

// Write Operation : When we_0 = 1, cs_0 = 1

always @ (address_0 or cs_0 or we_0 or data_0

or address_1 or cs_1 or we_1 or data_1)

begin : MEM_WRITE

if ( cs_0 && we_0 ) begin

mem[address_0] <= data_0;

end

else if (cs_1 && we_1) begin

mem[address_1] <= data_1;

end

end

// Tri-State Buffer control

// output : When we_0 = 0, oe_0 = 1, cs_0 = 1

assign data_0 = (cs_0 && oe_0 && !we_0) ? data_0_out : 8'bz;

// Memory Read Block

// Read Operation : When we_0 = 0, oe_0 = 1, cs_0 = 1

always @ (address_0 or cs_0 or we_1 or oe_0)

begin : MEM_READ_0

if (cs_0 && !we_0 && oe_0) begin

data_0_out <= mem[address_0];

end else begin

data_0_out <= 0;

end

对比同步,则类似于(伪代码,部分代码):

// Memory Write Block

// Write Operation : When we = 1, cs = 1

always @ (posedge clk)

begin : MEM_WRITE

if ( cs && we ) begin

mem[address] <= data;

end

end

// Memory Read Block

// Read Operation : When we = 0, oe = 1, cs = 1

always @ (posedge clk)

begin : MEM_READ

if (cs && !we && oe) begin

data_out <= mem[address];

/* oe_r <= 1;

end else begin

oe_r <= 0; */

end

end

可见,就是有没有使用时钟对数据进行同步的区分。

DRAM中的D为Dynamic,即动态,这是相对于static(静态)而言的,因为存在一种RAM叫SRAM,这里的静态是指只要保持充电,里面存储的数据就可以恒定保持,相比而言,动态就是DRAM里面存储的数据需要周期性的刷新,否则内部数据就会消失。

不过,无论是SRAM还是DRAM,都是RAM,只要断电,数据就会消失,因此它常常可以称为易失性存储器或者可变存储器等,以此来表明其存储特点。

回到SDRAM,这里的S就是指Synchronous了,总之同步说明了DRAM类型的行为。1996年底,SDRAM开始出现在系统中。与以前的技术不同,SDRAM旨在使其自身与CPU的时序同步。这使存储控制器能够知道请求数据准备就绪的确切时钟周期,因此CPU不再需要在两次存储访问之间等待。例如,PC66 SDRAM的运行速度为66 MT / s,PC100 SDRAM的运行速度为100 MT / s,PC133 SDRAM的运行速度为133 MT / s,依此类推。

SDRAM可以代表SDR SDRAM(单数据速率SDRAM),其中I / O,内部时钟和总线时钟相同。例如,PC133的I / O,内部时钟和总线时钟均为133 Mhz。单数据速率意味着SDR SDRAM在一个时钟周期内只能读/写一次。SDRAM必须等待上一个命令的完成才能执行其他读/写操作。

DDR的今生以及演变版本:DDR/DDR2/DDR3

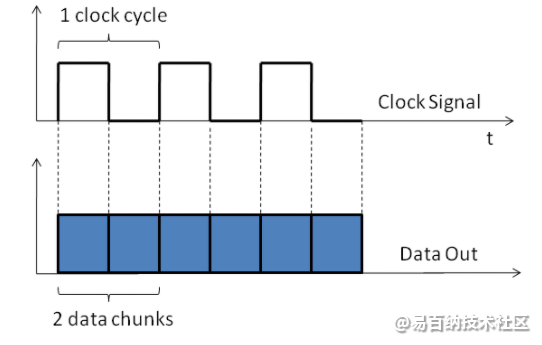

DDR,DDR2和DDR3基于SDRAM(同步动态随机存取存储器)设计的,这意味着它们使用时钟信号来进行同步。 DDR代表双倍数据速率,这意味着该类别的存储器每个时钟周期传输两个数据块。正是因为这个特点,这一类DDR(包括DDR2/DDR3)都标有它们可以运行的实际最大时钟速率的两倍,例如,DDR2-800内存工作在400 MHz,DDR2-1066和DDR3-1066内存工作在533 MHz,DDR3-1333内存工作在666.6 MHz,依此类推,这便是双倍数据速率SDRAM特点的体现。

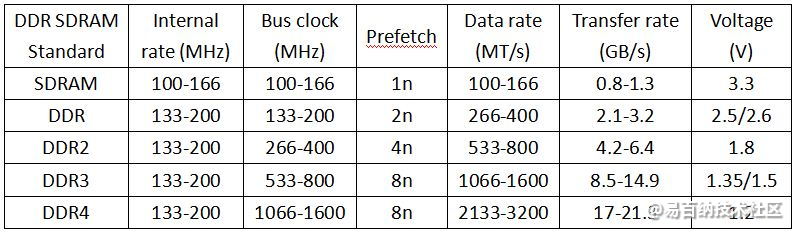

DDR/DDR2/DDR3/DDR4之间简单对比

下一代SDRAM是DDR,它通过在时钟信号的上升沿和下降沿传输数据来实现比以前的单数据速率SDRAM更大的带宽。实际上,它在不增加时钟频率的情况下将传输速率提高了一倍。DDR SDRAM的传输速率是SDR SDRAM的两倍,而无需更改内部时钟。DDR SDRAM作为第一代DDR存储器,预取缓冲区为2bit,是SDR SDRAM的两倍。DDR的传输速率在266〜400 MT / s之间。DDR266和DDR400属于这种类型。

不明白预取的含义暂时没有关系,后面或者后面博文我会专门提到的!

DDR2可以认为是下一代的DDR,它能够操作外部数据总线的速度是DDR的双倍。这是通过改善总线信号来实现的。DDR2的预取缓冲区是4位(DDR SDRAM的两倍)。DDR2内存与DDR具有相同的内部时钟速度(133〜200MHz),但是通过改进的I / O总线信号,DDR2的传输速率可以达到533〜800 MT / s。DDR2 533和DDR2 800存储器类型在市场上。

同理,DDR3是下一代的DDR2,,与当前的DDR2模块相比,DDR3内存降低了40%的功耗,从而允许更低的工作电流和电压(与DDR2的1.8 V或DDR的2.5 V相比,为1.5 V)。DDR3的传输速率为800〜1600 MT / s。DDR3的预取缓冲区宽度是8位,而DDR2的是4位,而DDR是2位。DDR3还添加了两个功能,例如ASR(自动自刷新)和SRT(自刷新温度)。它们可以使存储器根据温度变化来控制刷新率。

DDR4 SDRAM提供较低的工作电压(1.2V)和较高的传输速率。DDR4的传输速率为2133〜3200 MT / s。DDR4增加了四种新的Bank Groups技术。每个Bank Group都具有单手操作的功能。DDR4可以在一个时钟周期内处理4个数据,因此DDR4的效率明显优于DDR3。DDR4还增加了一些功能,例如DBI(数据总线倒置),CRC(循环冗余校验)和CA奇偶校验。它们可以增强DDR4存储器的信号完整性,并提高数据传输/访问的稳定性。

上述只是粗略的对比,下面来分门别类谈谈它们之间的差异。

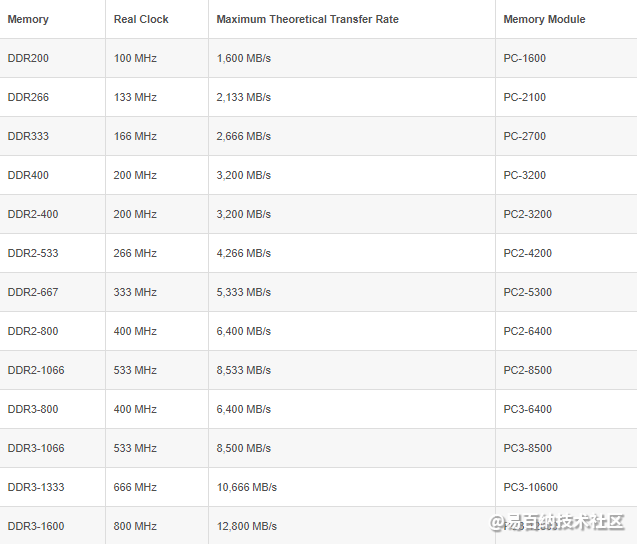

上文中,我们举了一个例子:

DDR2-800内存工作在400 MHz,DDR2-1066和DDR3-1066内存工作在533 MHz,DDR3-1333内存工作在666.6 MHz。

要注意,这些时钟速率是内存可以正式使用的最大频率。无论如何,这并不意味着内存会自动以这些“速度”工作。

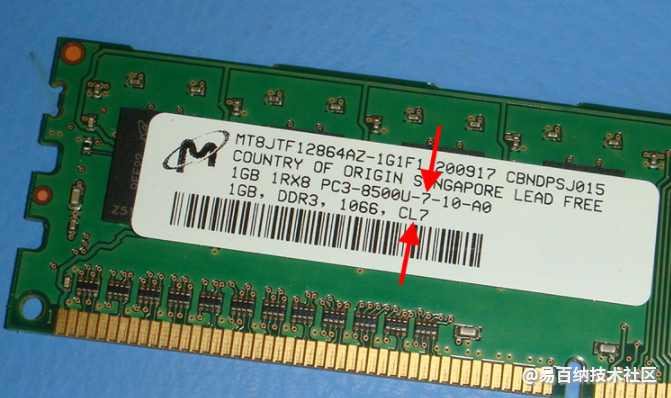

从理论上讲,该命名系统DDRx-yyyy(其中x是技术世代,yyyy是DDR时钟速率)仅用于存储芯片。内存模块(用于焊接内存芯片的小印刷电路板)使用不同的命名系统:PCx-zzzz,其中x是技术代号,zzzz是最大理论传输速率(又称最大带宽)。假设在每个单个时钟脉冲上都会传输数据,则该数字为我们提供了每秒可以在存储控制器和存储模块之间传输多少字节的信息。通过将以MHz为单位的DDR时钟乘以8可以轻松完成此数学运算(实际上,真正的数学运算是通过乘以64,然后除以8来完成的。 由于64/8 = 8,我们可以简单地乘以八来获得相同的结果。)。这将为我们提供最大的理论传输速率,以MB / s(兆字节/秒)为单位。例如,DDR2-800存储器的最大理论传输速率为6,400 MB / s(800 x 8),使用这种存储器的存储器模块称为PC2-6400。在某些情况下,数字是四舍五入的。例如,DDR3-1333存储器的最大理论传输速率为10,666 MB / s,但是根据制造商的不同,使用这种存储器的存储器模块称为PC3-10666或PC3-10600。

了解这些数字是最大理论数字,而且从未达到它们,这一点非常重要。发生这种情况的原因是,出于数学考虑,我们假设内存将在每个时钟周期内将数据发送到内存控制器,而这种情况根本不会发生。内存控制器和内存需要交换命令(例如,指示内存传递给定位置的数据的命令),在此期间内存将不会传输数据。

速度对比

DDR,DDR2和DDR3之间的主要区别之一是每一代都能达到的最高传输速率。下面我们列出了每一代最常见的速度。一些制造商可以提供能够达到所列速度之外的其他速度的存储芯片,例如,针对超频者的专用存储器。结束于33和66 MHz的时钟实际上是周期性的十进制扩展(分别为33.3333和66.6666)。

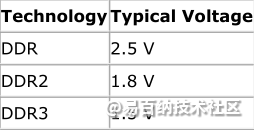

电压对比

DDR3存储器的工作电压低于DDR2存储器,而DDR2存储器的工作电压则低于DDR存储器。这意味着DDR3存储器比DDR2存储器消耗更少的功率,而DDR2存储器又比DDR存储器消耗更少的功率。通常,DDR存储器的供电电压为2.5 V,DDR2存储器的供电电压为1.8 V,而DDR3存储器的供电电压为1.5 V(尽管需要1.6 V或1.65 V的模块是通用的,将来仅需要1.35 V的芯片也将变得通用)。某些内存模块可能需要比列出的更高的电压。这种情况尤其发生在支持时钟频率高于官方频率的内存(即针对超频的内存)上。

延迟对比

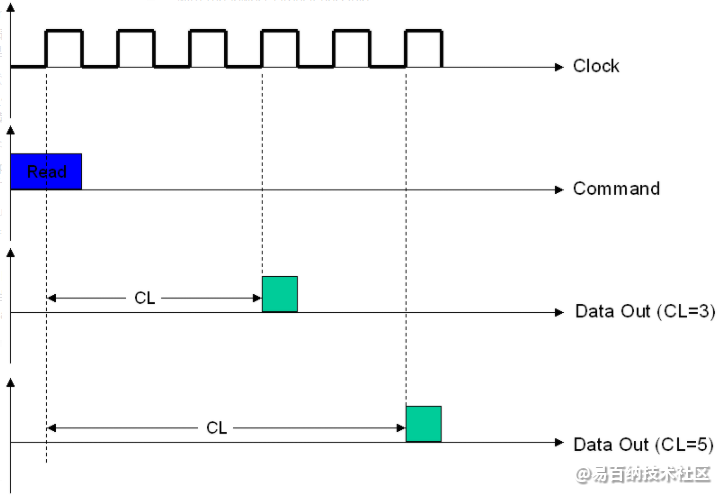

延迟是内存控制器在请求数据与实际发送数据之间必须等待的时间。也称为CAS(列地址选通)延迟或简称CL。该数字以时钟周期表示。例如,带有CL3的内存意味着内存控制器必须等待三个时钟周期,直到发出请求后才传送数据。对于带有CL5的内存,内存控制器将不得不等待更多:五个时钟周期。因此,您始终应寻找具有尽可能低延迟的内存模块。

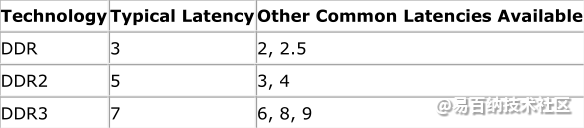

DDR3存储器具有比DDR2存储器更高的延迟,而DDR2存储器又具有比DDR存储器更高的延迟。 DDR2和DDR3存储器具有一个称为AL(附加延迟)或简称A的附加参数。对于DDR2和DDR3存储器,总延迟将为CL + AL。幸运的是,几乎所有DDR2和DDR3内存都为AL 0,这意味着不需要额外的延迟。下面我们总结了最常见的延迟值。

这意味着与DDR2存储器相比,DDR3存储器延迟更多的时钟周期来开始传送数据(就像DDR2存储器相比DDR2存储器延迟更多的时钟周期来开始传送数据),但这并不一定意味着更长的等待时间(这是正确的)仅当比较以完全相同的时钟频率工作的内存时)。例如,与DDR3-800 CL7存储器相比,DDR2-800 CL5存储器将延迟更少的时间(即更快)来开始传送数据。但是,由于两者都是“ 800 MHz”存储器,因此两者都提供了完全相同的最大理论传输速率(6,400 MB / s)。同样重要的是要记住,DDR3内存将比DDR2内存消耗更少的电量。

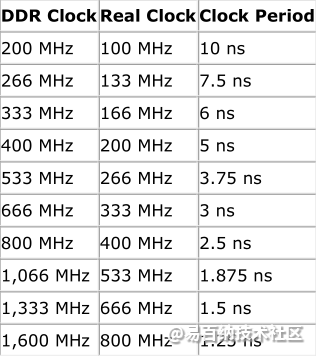

当比较具有不同时钟速率的模块时,您需要做一些数学运算才能比较延迟。请注意,我们正在谈论“时钟周期”。当时钟较高时,每个时钟周期较短(即较低的周期)。例如,在DDR2-800内存上,每个时钟周期需要2.5 ns,数学很简单,周期= 1000 /频率(请注意,您需要使用实际时钟,而不是DDR。为方便起见,我们在下面提供了一个参考表。因此,假设具有CL 5的DDR2-800内存,此初始等待时间相当于12.5 ns(2.5 ns x 5)。现在假设一个带CL 7的DDR3-1333内存。有了这个内存,每个时钟周期的周期为1.5 ns(请参见下表),因此总等待时间(等待时间)将为10.5 ns(1.5 ns x 7)。因此,即使此DDR3内存的等待时间似乎更长(7 vs. 5),等待时间实际上也更短。因此,请不要以为DDR3内存的延迟要比DDR2内存的慢:这将取决于您所讨论的时钟速率。

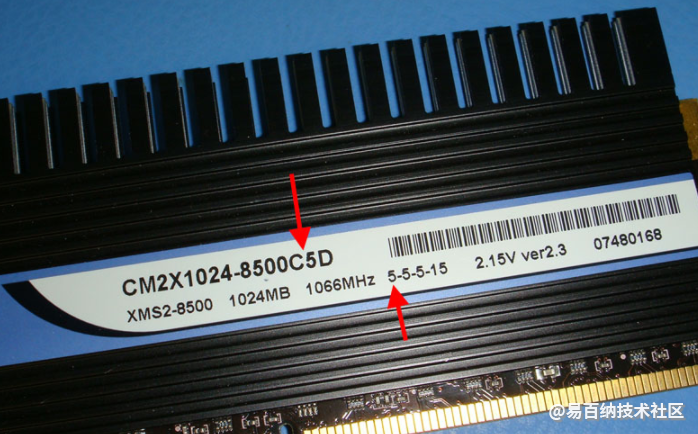

通常,制造商会以一系列由破折号隔开的数字来宣布存储时序(例如5-5-5-5、7-10-10-10等)。 CAS延迟始终是这些序列中的第一个数字。

预取差异

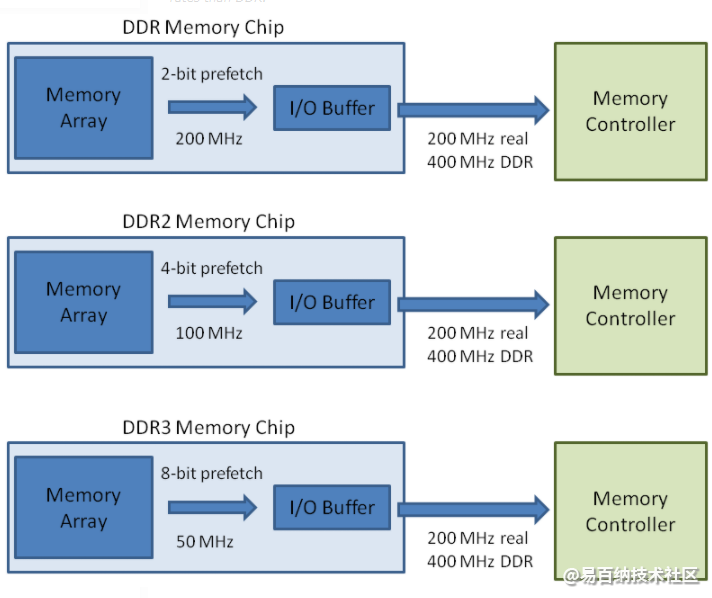

动态存储器将数据存储在微型电容器阵列中。 DDR存储器在每个时钟周期将两位数据从存储器阵列传输到存储器内部I / O缓冲区。这称为2位预取。在DDR2上,此内部数据路径增加到4位,在DDR3上,它再次增加到8位。实际上,这是使DDR3以高于DDR2的时钟速率工作,并使DDR2以高于DDR的时钟速率工作的技巧。到目前为止,我们所指的时钟是“外部世界”上的时钟速率,即来自存储器的I / O接口上的时钟速率,存储器与存储器控制器之间进行通信。但是,在内部,内存的工作方式略有不同。

为了更好地理解这个想法,我们比较一下DDR-400,DDR2-400和DDR3-400内存芯片(我们知道DDR3-400内存不存在,但假装确实存在)。这三款芯片以200 MHz的频率在外部工作,每个时钟周期传输两个数据,从而获得了外部性能,就好像它们以400 MHz的频率工作一样。但是,在内部,DDR芯片在内存阵列和I / O缓冲区之间传输两位,因此,为了匹配I / O接口速度,此数据路径必须在200 MHz(200 MHz x 2 = 400 MHz)下工作。由于在DDR2上该数据路径从两位增加到了四位,因此它可以以一半的时钟速率工作,以实现相同的性能(100 MHz x 4 = 400 MHz)。使用DDR3时,会发生同样的事情:数据路径再次加倍至8位,因此它可以以DDR2的一半时钟速率或仅DDR时钟速率的1/4工作,以实现相同的性能(50 MHz x 8 = 400 MHz)。

将每一代的内部数据路径加倍意味着,每一个新的存储器一代都可以预见其芯片模型的最大时钟速率是前一个芯片的两倍。例如,在DDR-400,DDR2-800和DDR3-1600内存上,内存在内部以相同的时钟频率(200 MHz)工作。

电阻端接对比

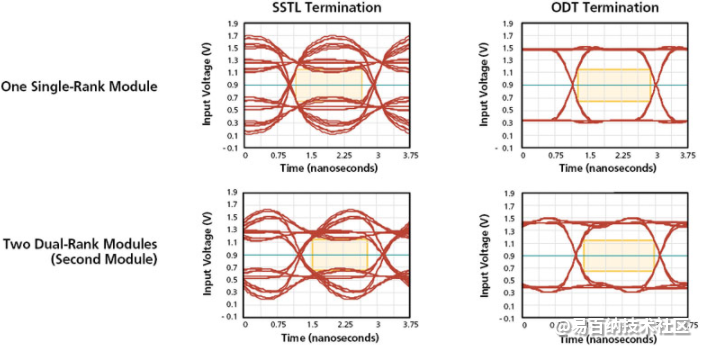

在DDR存储器上,必要的电阻端接位于主板上,而在DDR2和DDR3存储器上,此端接位于内存芯片内部-这种技术称为ODT,即管芯端接。这样做是为了使信号“更干净”。在下图,您可以看到到达存储芯片的信号。在左侧,您可以看到使用主板终端(DDR存储器)的系统上的信号,而在右侧,您可以看到使用裸片终端(DDR2和DDR3存储器)的系统上的信号。即使是外行,也可以轻易地说出右侧的信号比左侧的信号更干净,更稳定。在黄色正方形上,您可以比较时间范围的差异–该时间范围是内存必须读取或写入一条数据的时间。通过使用片上终端,此时间范围变得更宽,由于存储器有更多时间读取或写入数据块,因此可以实现更高的时钟。

物理方面对比

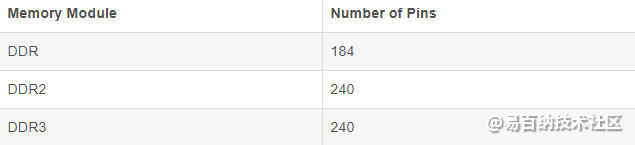

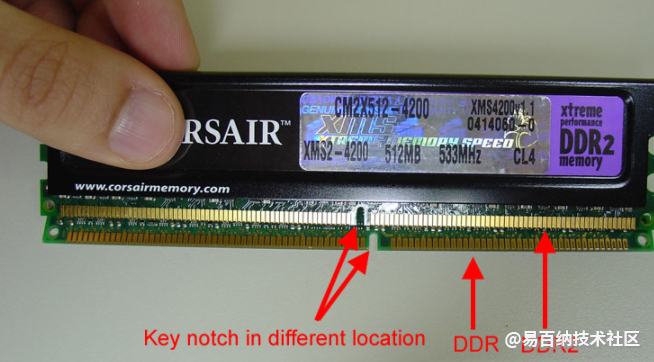

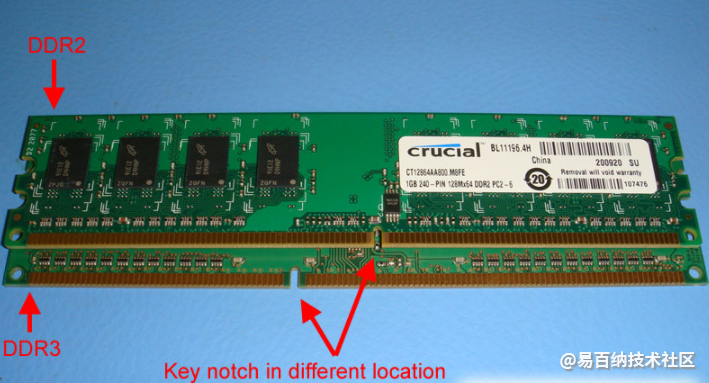

最后,我们有物理层面的差异。你买的内存芯片已经焊接在一块印刷电路板上,称为 "内存模块"。每个DDRgeneration的内存模块在物理上都是不同的,所以比如你无法将DDR2模块安装在DDR3插座上。除非你的主板同时支持DDR2和DDR3插槽(只有少数主板支持),否则你无法从DDR2升级到DDR3,除非更换主板,最终更换CPU(如果在你的系统中,内存控制器是嵌入在CPU中的,就像所有AMD和Intel的Core i7处理器一样)。同样的事情也适用于DDR和DDR2。除了少数罕见的例外,你不能用DDR2替换DDR内存。DDR2和DDR3模块具有相同的引脚数,但是,键槽的位置不同。

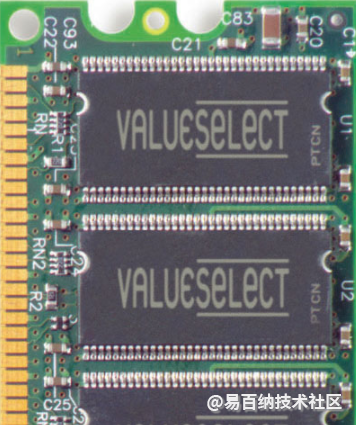

所有DDR2和DDR3芯片都使用BGA(球栅阵列)封装,而DDR芯片几乎总是使用TSOP(薄小外形封装)封装。市场上有几种采用BGA封装的DDR芯片(例如Kingmax的DDR芯片),但并不常见。在下图中,您可以看到DDR模块上的TSOP芯片的外观:

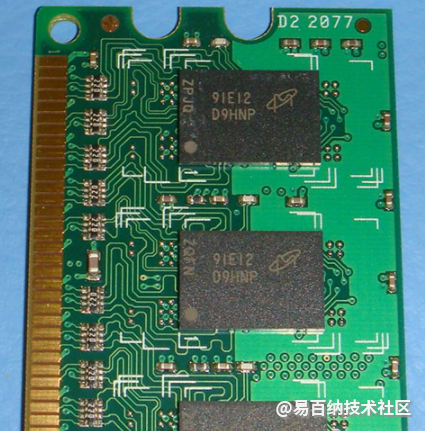

而在下图中,您可以看到DDR2上的BGA芯片的外观。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:7746次2021-01-31 01:07:50

-

浏览量:8016次2021-01-30 23:18:56

-

浏览量:6461次2021-01-31 04:24:47

-

浏览量:9127次2021-02-06 22:29:19

-

浏览量:11329次2020-12-13 19:59:59

-

浏览量:20270次2020-12-06 18:59:36

-

浏览量:9149次2020-12-27 18:30:21

-

浏览量:5816次2021-04-03 14:12:54

-

浏览量:9372次2021-01-09 02:07:52

-

浏览量:11614次2021-01-17 00:16:33

-

浏览量:5692次2021-03-18 22:57:24

-

浏览量:14621次2021-01-01 02:53:29

-

浏览量:7527次2021-03-14 02:34:44

-

浏览量:13475次2021-01-02 00:02:19

-

浏览量:7646次2021-01-23 18:45:14

-

浏览量:7943次2021-03-15 23:18:36

-

浏览量:5741次2021-05-23 23:50:14

-

浏览量:6323次2021-03-17 23:24:53

-

浏览量:5895次2021-03-14 01:58:15

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友