FPGA的设计艺术(9)FPGA开发技巧与工程管理

前言

阅读一段话:

产品开发工程师对公司的未来成功与产品对当前的成功一样重要。将工程师,受过高等教育的技术专家视为商品,会降低团队士气,并不可避免地影响项目进度和质量。在竞标一个项目以赢得业务的情况下,期望或要求工程师无偿加班来弥补差额并不是公司长期成功的途径。

是不是深有同感,这是工程管理理念的一部分,本文最后提出了一系列值得每个公司管理者需要长远考虑的问题,你要打造一个什么样的团队乃至公司?你要如何管理?

在此之前,还是先看有关FPGA开发有关的内容,这是工程师、开发者的日常。

设计技巧和常见错误

FPGA开发包括数字设计,代码设计和印刷电路板(PCB)设计元素。以下段落介绍了这些领域中的一些最佳做法和常见错误。

PCB设计

-

设备配置:确定FPGA配置源和JTAG访问的方法。 JTAG链中允许有多个设备(当链中的设备不是来自同一家族或制造商时,请格外小心)。确保访问配置模式控制引脚。

-

时钟输入引脚:专用时钟输入引脚可轻松访问内部全局时钟布线资源。

-

供应商IP引脚:在PCB布局之前构建供应商IP。诸如DRAM控制器之类的复杂IP具有非常特殊的时序和PCB布局约束。 PCB设计人员使用工具生成的引脚分配,并进行尽可能少的更改。任何更改都将反馈到综合工具以验证可接受性。在PCB制造之前执行此操作。

-

数据流。考虑通过FPGA传输的数据。某些FPGA架构在一定方向上的数据传输效率更高,例如从左到右,进位从上到下移动。分配用于物理架构的引脚可以提高资源使用效率。

-

电气标准。尽管FPGA有多个IO库,但是在单个库中可以混合使用哪些IO标准是有限制的。尝试在FPGA Bank中混合不兼容的IO标准是一个常见错误,在PCB布局完成后很难发现。

-

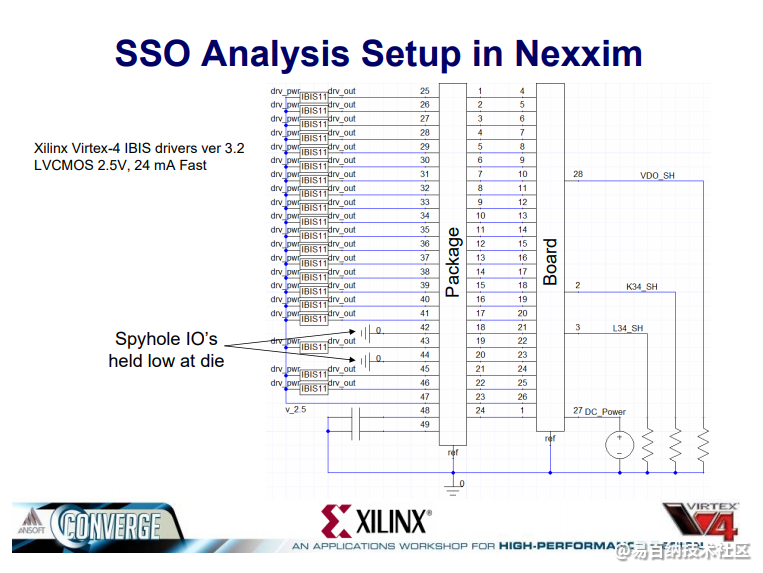

同步开关输出(SSO):每个IO bank的汲取电流量受到限制。如果同时更改太多输出,则bank可能需要的电流超过可用电流。使用Xilinx Virtex-4 FPGA的同步开关输出(SSO)分析是对此主题的一个很好的展示。

上述链接截图:

-

功耗分配:阅读并注意有关电源电压,sequencing和去耦的制造商建议。

-

调试支持:测试连接器与设计中最大的总线一样大,加上一些控制信号,可以在integration过程中提供令人难以置信的洞察力。

数字设计

有些工程师似乎认为,HDL让他们编写的软件可以神奇地成为FPGA中的数字设计。其实不然。数字设计技术是开发FPGA的关键技能。无论使用哪种工具或语言,糟糕的数字设计都会导致糟糕的产品。

下面给出几条数字设计的建议:

-

层次结构:将设计分成足够小的单元,以用描述其作用的名称进行标记。

-

模块设计:一个常见的错误是无效的模块或接口定义。

-

跨时钟域(CDC)。每个设计单元或组件应具有一个时钟(如果设计单元具有多个时钟,则需要跨时钟)。在设计单元之间移动数据和/或信号需要特别注意CDC。

-

同步设计:FPGA需要同步设计技术。所有FPGA制造商都建议同步设计。如果您的设计不同步,则制造商的支持人员将竭诚为您提供帮助。同步设计消除了通过不同逻辑路径与速度变化相关的问题。通过以规定的时间间隔对信号进行采样,可以以简单的方式处理快路径和慢路径。它们在各种工艺,电压和温度(PVT)的变化中都能很好地工作,并且易于迁移到新技术。 Bob Zeidman在《 CPLD和FPGA设计简介》中介绍了一套简洁的同步设计规则。

- 同步设计简单的说就是所有的数据都通过组合逻辑和触发器,同步到一个时钟上。

- 延迟始终由触发器控制,而不是组合逻辑。

- 任何由组合逻辑产生的信号,如果不先经过同步触发器,就不能反馈到同一组组合逻辑中。

- 时钟不能被门控--换句话说,时钟必须直接进入触发器的时钟输入,而不需要经过任何组合逻辑。

- 系统只有一个时钟。不要为实体或进程提供其他实体或进程的输出时钟。(这里是VHDL里的说法,在Verilog中可以理解为一个模块(无论多小的模块)的输出不能作为另一个模块的时钟)。

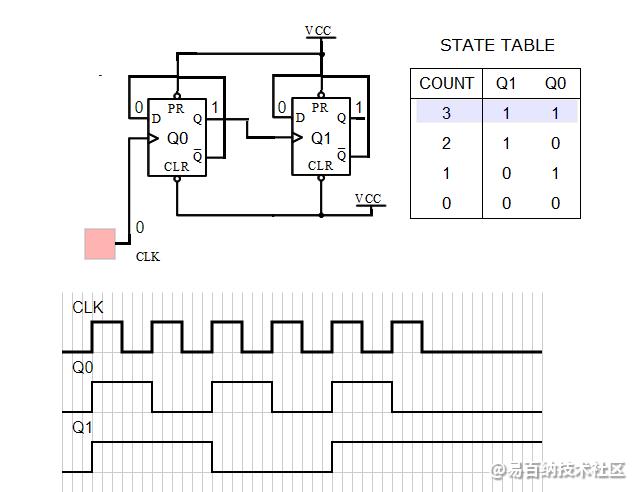

同步设计计数器示例:纹波计数器

纹波计数器使用一个电路的数据输出作为另一电路的时钟输入。这违反了规则5;不要为另一个电路的输出提供时钟。这种非同步设计使用较少的逻辑进行计数,并且在时钟速度较慢时还可以,但在时钟速度较高时可能会造成灾难性的后果。考虑到在Fclk = 100MHz(Tclk = 10ns)和Tpd = 1ns的情况下,一个12级波纹计数器将在多个时钟周期内改变位!产生的故障输出是确定性的。

减少编码时的不确定性。

避免这样做,因为它会导致潜在的缺陷。在开始在HDL中编码设计之前,你应该对你想要的功能有一个清晰的了解。

Verilog/VHDL编码

- 推断的锁存器:推断的锁存器警告是工具告诉你,设计者没有有效地传达他们的意图。为了完成所描述行为的等式,工具必须添加一个设计者没有要求的内存元素! 通过在进程中为信号分配默认值(case),并在if语句中加入 else子句来避免这种情况。

- 敏感列表

- 变量:可合成的HDL不是软件。变量可以是功能强大的工具,但它们可以吸引那些无所顾忌的人来编写软件,而不用描述数字设计。如果有变量,请查找错误。

参考:

仿真

仿真需要花更多的时间,但是投资回报率很高。主要的好处是,在进行上板之前,您知道FPGA功能是正确的。

为什么仿真?

功能仿真证明,HDL描述的设计符合要求。在实验室中验证硬件功能的工作量很大。由于对FPGA的可见性有限,因此很难调试。在仿真过程中,您几乎可以无限了解设计。在仿真过程中查找设计或编码错误要比在实验室上板过程中快得多。

-

系统模型:当仿真与FPGA外部部件通信的数字设计时,仿真需要外部部件的模型。当开发这些系统模型时,其理念是围绕着合理的真实性。 如果你只是简单地测试一个SPI接口,一个非常简单的模型就可以了。

-

时序:功能仿真告诉我们故事的第一部分。来自综合工具的静态时序分析表明,设计将或不会以所需的时钟速度运行。这些工具需要与时钟相关的约束定义。

-

花费多久仿真:在Xilinx Virtex-5设备中使用诸如以太网MAC之类的硬IP时,运行涉及MAC IP的仿真几乎没有意义。这种仿真需要花费大量时间,并且您不能修改IP来纠正任何缺陷。(此外,它已经由制造商和许多设计进行了广泛的测试。)

有关仿真的更多内容,仿真技巧以及注意事项,可以参考我的其他博客:

FPGA设计心得(10)关于行为仿真的一点观点

工程管理

工程就是生意,而生意就是关系。因此,成功的工程是关于建立高质量的关系。项目通常不会因为技术原因而失败。他们失败的原因是开发团队中的人的行为。

许多工程师声称他们不关心营销,尽管这是让他们就业的原因。利润是企业持续经营活动的要求,与营销密切相关。一个公司最强的营销是高质量、有良好记录(读作:可维护)的产品。所有的工程师都应该朝着这个目标努力。这就是你如何为你的公司、你的团队、你自己建立声誉。你的声誉强烈地影响着你的下一份工作;或者说缺乏声誉。

制作的文档中出现句子碎片。错别字也会让人怀疑你的专业性。这是一个竞争激烈的世界;不要提供理由来质疑你对细节的关注。

管理工程师

- 生产力:在PeopleWare中,DeMarco和Lister确定,长时间不间断的活动会大大提高工作效率。在经历了一天的持续中断(会议、电子邮件、电话等)之后,人们可能会一无所获地离开。这损害了计划和预算,但更重要的是它损害了士气。

注: T. DeMarco and T. Lister. Peopleware - Productive Projects and Teams. 1999.

- 培训:工学院提供科学和数学基础知识,但确实为我们做好了在工作中学习的准备。向工程师提出他不熟悉的问题类型时,讲师指导的培训可以明显缩短学习曲线。

- 团队。团队凝聚力和个人积极性是项目成功的关键。等于或大于技术挑战。所有学科之间的团队凝聚力至关重要。如果项目失败,那么FPGA的设计完美程度将无关紧要。

- 公司价值。产品开发工程师对公司的未来成功与产品对当前的成功一样重要。将工程师,受过高等教育的技术专家视为商品,会降低团队士气,并不可避免地影响项目进度和质量。在竞标一个项目以赢得业务的情况下,期望或要求工程师无偿加班来弥补差额并不是公司长期成功的途径。

- 工作满意度。给工程师一个有趣的问题,一个解决问题的资源,尽可能少的干扰和烦恼,使他们的工作满意度很高。幸运的是,培养工程师的自我价值相对容易。一副大显示器要花几百美元。考虑到由于信息可用性而带来的效率提高以及士气和动力的提高,投资回报率是相当不错的。

- 时间规划。时间规划预估是有关事件何时发生的最佳猜测。将来距离越远,准确性越低。您必须定期修改长期计划。要求员工付出巨大的个人牺牲才能满足任意计划,这是长期企业灾难的良方。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:6922次2021-02-14 01:58:16

-

浏览量:4906次2021-03-12 23:39:20

-

浏览量:5893次2021-03-14 01:58:15

-

浏览量:8836次2021-02-07 00:59:28

-

浏览量:5065次2021-06-20 20:10:03

-

浏览量:6472次2021-04-27 00:06:35

-

浏览量:5740次2021-05-23 23:50:14

-

浏览量:10622次2021-02-20 17:50:13

-

浏览量:8607次2021-04-10 01:44:48

-

浏览量:6095次2021-03-14 01:12:39

-

浏览量:13158次2021-05-23 01:13:25

-

浏览量:5093次2021-04-27 00:05:09

-

浏览量:7525次2021-03-14 02:34:44

-

浏览量:7746次2021-01-31 01:07:50

-

浏览量:5303次2021-05-17 23:44:33

-

浏览量:7941次2021-03-15 23:18:36

-

浏览量:10139次2021-03-21 22:58:26

-

浏览量:6718次2021-03-22 01:26:53

-

浏览量:7183次2021-03-22 00:49:53

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友