FPGA的设计艺术(3)静态时序分析

什么是静态时序分析(STA)?

静态时序分析介绍

静态时序分析(STA)是一种通过检查所有可能的路径是否存在时序违规来验证设计时序性能的方法。 STA将设计分解为时序路径,计算沿每个路径的信号传播延迟,并检查设计内部和输入/输出接口处时序约束的违反情况。

静态时序分析与动态仿真的优缺点

执行时序分析的另一种方法是使用动态仿真,它可以针对给定的一组输入激励矢量确定电路的完整行为。 与动态仿真相比,静态时序分析要快得多,因为不需要仿真电路的逻辑操作。 STA也更彻底,因为它检查所有时序路径,而不仅仅是检查一组测试向量所敏感的逻辑条件。 但是,STA只能检查电路设计的时序,而不能检查其功能。

STA如何工作?

时序路径

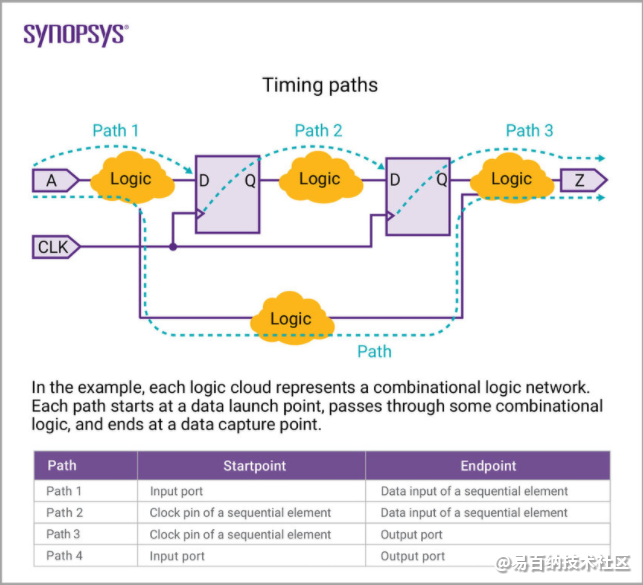

在执行时序分析时,STA首先将设计分解为时序路径。 每个时序路径均包含以下元素:

- 起点: 时序路径的开始,在该时序中,数据由时钟有效沿(上升沿或者下降沿都有可能)。 每个起点必须是输入端口或寄存器时钟引脚。

- 组合逻辑网络: 没有内存或内部状态的元素。 组合逻辑可以包含AND,OR,XOR和反相器元素,但不能包含触发器,锁存器,寄存器或RAM。

- 终点: 时序路径的末尾,其中数据由时钟沿捕获或在特定时间必须可用。 每个端点必须是寄存器数据输入引脚或输出端口。

下图显示了一个简单设计示例中的时序路径:

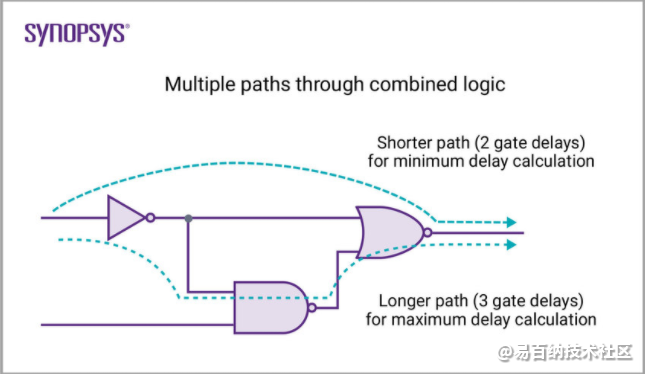

组合逻辑路径可能包含多个路径,如下图所示。 STA使用最长的路径来计算最大延迟,而使用最短的路径来计算最小延迟。

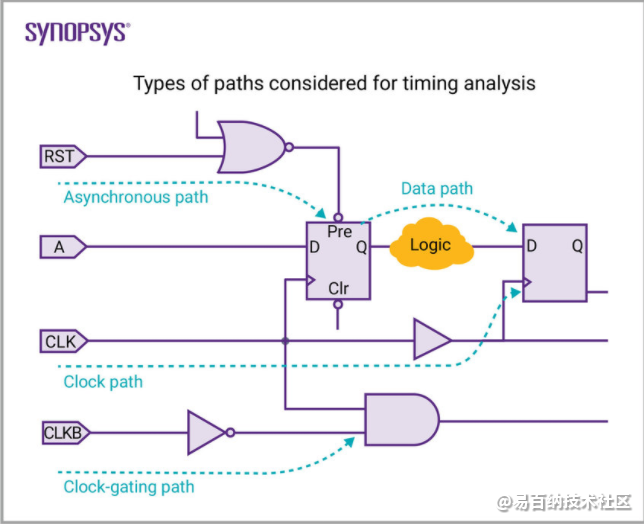

STA还考虑以下类型的时序分析路径:

- 时钟路径: 从时钟输入端口或单元引脚通过一个或多个缓冲器或反相器到时序元件的时钟引脚的路径; 用于数据设置和保持检查。

- 时钟门控路径: 从输入端口到时钟门控元件的路径; 用于时钟门控设置和保持检查。

- 异步路径: 从输入端口到时序元素的异步置位(asynchronous set)或清除(clear)引脚的路径; 用于recovery和removal检查。

延迟类型

将设计分解为一组时序路径后,STA工具将计算沿每个路径的延迟。 一条路径的总延迟是该路径中所有单元延迟和布线延迟的总和。

-

单元延迟是路径中从逻辑门的输入到输出的延迟量。 如果没有来自SDF文件的带批注的延迟信息,该工具将从逻辑库中为单元提供的延迟表计算单元延迟。

通常,延迟表会根据一个或多个变量(例如输入转换时间和输出负载电容)来列出延迟量。 该工具从这些表条目中计算每个单元延迟。 -

布线延迟延迟是指时序路径中从一个单元的输出到下一个单元的输入的延迟量。 这种延迟是由于两个单元之间互连的寄生电容,净电阻和驱动网络的单元有限的驱动强度所引起的。

建立与保持时间

然后,STA检查违反时序约束的情况,如建立和保持约束。

- 建立约束规定了在捕获设备(时序设备)中的数据的时钟边沿之前,数据在时序设备的输入端需要多少时间。该约束强制执行数据路径上相对于时钟边沿的最大延迟。

- 保持约束指定了在捕获设备中的数据的时钟边沿之后,数据在时序设备的输入端保持稳定所需的时间。该约束强制要求数据路径上相对于时钟边沿的最小延迟。

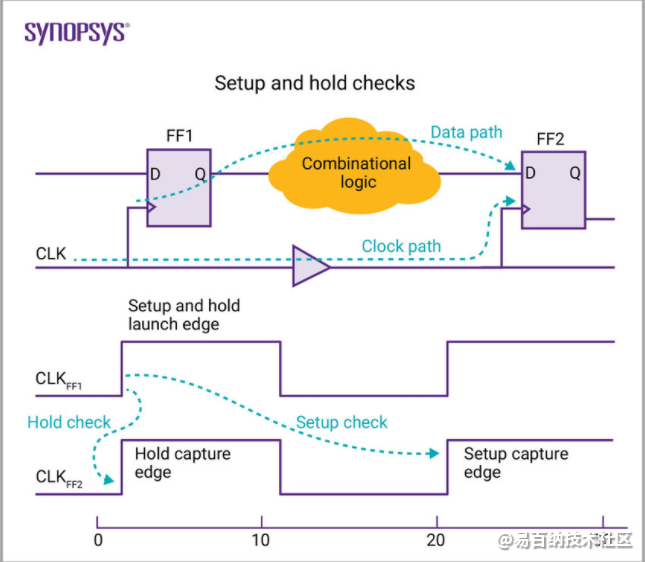

下面的例子显示了STA如何检查触发器的设置和保持约束。

在这个例子中,假设触发器在逻辑库中定义为最小建立时间为1.0时间单位,最小保持时间为0.0时间单位。时钟周期在工具中定义为10个时间单位。时间单位大小,如ns或ps,在逻辑库中指定。

默认情况下,该工具假设信号在一个时钟周期内通过每个数据路径传播。 因此,当工具执行建立检查时,它会验证从FF1发起的数据在一个时钟周期内到达FF2,并且在数据被FF2的下一个时钟边沿捕获之前至少到达1.0个时间单位。如果数据路径延迟过长,则报告为时序违规。 对于该建立检查,工具考虑沿数据路径的最长可能延迟和沿FF1和FF2之间的时钟路径的最短可能延迟。

当工具执行保持检查时,它验证从FF1发起的数据到达FF2的时间不早于上一个时钟周期的捕获时钟边沿。 该检查确保已经存在于FF2的输入端的数据在捕获上一个周期数据的时钟边沿之后保持足够长的稳定时间。对于该保持检查,该工具考虑沿数据路径的最短延迟和沿FF1和FF2之间的时钟路径的最长延迟。如果时钟路径有较长的延迟,就会发生保持违规。

如果某些路径不打算按照STA工具默认的建立和保持行为运行,则需要将这些路径指定为时序例外。否则,该工具可能会错误地将这些路径报告为唏嘘异常。

STA工具可以让您指定以下类型的异常。

- 伪路径(False Path):由于逻辑配置、预期的数据序列或工作模式而从未被感应的路径。

- 多周期路径。从发射到捕获需要一个以上的时钟周期的路径。

- 最小或最大延迟路径。必须满足您明确指定为时间值的延迟约束的路径。

总结

本文参考静态时序分析的专业工具公司Synopsys提供的资料,但不妨碍对于FPGA中的静态时序分析的理解,都是大同小异,甚至可以说是一致的。

在FPGA中,静态时序分析更为简单,只需要在综合工具的GUI界面中进行时序约束,综合实现可以查看静态时序分析结果。根据结果了解设计的时序,进而修改设计或者修改约束等,这是一个迭代的过程。

注意,可以再GUI界面中进行约束时序,也可以直接使用Tcl语言进行约束,本质上都会转换为Tcl约束,存储于*dc文件中。这里有一个却别,Xilinx早期的综合工具ISE的约束文件是UCF文件,使用的不是TCL语言,后面的Vivado使用的XDC文件,对SDC进行了自己的扩展。Synopsys或者Intel的工具的约束文件都是sdc文件,这里所谓的文件指的是文件的后缀。

例如,Xilinx的XDC文件:

################################################################################

## XDC generated for xc7k325t-ffg900-1 device

# 125.0MHz GT Reference clock constraint

create_clock -name GT_REFCLK1 -period 8.0 [get_ports GTXQ0_P]

####################### GT reference clock LOC #######################

set_property LOC R7 [get_ports GTXQ0_N]

set_property LOC R8 [get_ports GTXQ0_P]

# USER_CLK Constraint : Value is selected based on the line rate (3.125 Gbps) and lane width (4-Byte)

# create_clock -name user_clk_i -period 12.800 [get_pins aurora_module_i/clock_module_i/user_clk_buf_i/I]

# 20.0 ns period Board Clock Constraint

create_clock -name init_clk_i -period 20.0 [get_ports INIT_CLK_P]

# 20.000 ns period DRP Clock Constraint

create_clock -name drp_clk_i -period 20.000 [get_ports DRP_CLK_IN]

###### CDC in RESET_LOGIC from INIT_CLK to USER_CLK ##############

set_false_path -to [get_pins -filter {REF_PIN_NAME=~*D} -of_objects [get_cells -hierarchical -filter {NAME =~ *aurora_8b10b_0_cdc_to*}]]静态时序分析是芯片设计以及FPGA开发的重点难点,十分重要,这个专题的文章在学生时期也零零散散写了一些,例如:

水平有限,仅供参考。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:7146次2021-02-21 16:01:28

-

浏览量:6794次2021-02-21 21:08:27

-

浏览量:6720次2021-03-22 01:26:53

-

浏览量:7994次2021-02-21 01:20:21

-

浏览量:6925次2021-02-14 01:58:16

-

浏览量:5895次2021-03-14 01:58:15

-

浏览量:8839次2021-02-07 00:59:28

-

浏览量:10962次2021-02-20 22:37:06

-

浏览量:6476次2021-04-27 00:06:35

-

浏览量:5069次2021-06-20 20:10:03

-

浏览量:4778次2021-03-13 01:55:14

-

浏览量:4909次2021-03-12 23:39:20

-

浏览量:5741次2021-05-23 23:50:14

-

浏览量:8016次2021-01-30 23:18:56

-

浏览量:6097次2021-03-14 01:12:39

-

浏览量:5097次2021-04-27 00:05:09

-

浏览量:7528次2021-03-14 02:34:44

-

浏览量:7943次2021-03-15 23:18:36

-

浏览量:13161次2021-05-23 01:13:25

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友