技术专栏

innovus dbGet命令的使用

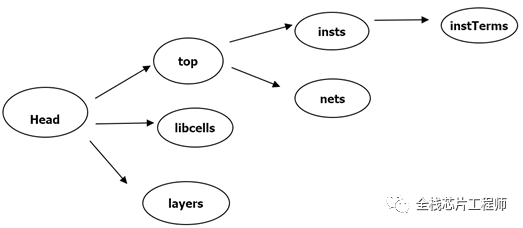

dbGet是基于一种树状的结构图,如下图所示。head是最原始的parent,然后我们需要寻找的object就藏在这每一个一级一级的分支下。selected和top其实也属于head的一个分支,只不过它们比较常用,所以就单独列出作为一个原始分支。现在各种object一共加起来有64个,我们需要做的就是找准路线,一击必中,把“指针”找出来。

dbGet的用法就像Tcl一样,是很灵活多变的,体现在它这个命令本身具有很多option

dbGet

[-p num ]

[-u]

[-regexp]

[-d]

{ obj | objList | head | top | selected}

[. objType ]…[. attrName | .? | .?? |.?h]

[ pattern ]

[expression]

[-v]

[-e]

[-i]

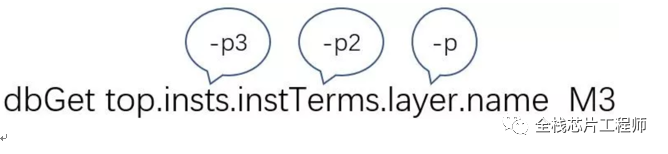

-p是我们经常用到的option。p指point,有时我们使用dbGet筛选得到我们所想要的结果。但更多时候,这些结果会被用来做另一个层级的dbGet指令。这时候就要用到-p,来返回指针。

如果我们想要知道所有在M3上的insts pin的名字:

innovus 59> dbGet [dbGet -p2 top.insts.instTerms.layer.name M3].name

CHIP_TOP/buf_input_datax2x/AREPEATER_datax2x/Z ……

给出几个例子:

-

列出设计中所有place/unplace的instance

<pre class="code-snippet__js" data-lang="css">```

<span class="code-snippet_outer"><span class="code-snippet__selector-tag">dbGet</span> <span class="code-snippet__selector-attr">[dbGet -p top.insts.pStatus unplaced]</span><span class="code-snippet__selector-class">.name</span></span>dbGet [dbGet -p top.insts.pStatus placed].name

-

List all fixed instances in the design

<pre class="code-snippet__js" data-lang="css">```

<span class="code-snippet_outer"><span class="code-snippet__selector-tag">dbGet</span> <span class="code-snippet__selector-attr">[dbGet -p top.insts.pStatus fixed]</span><span class="code-snippet__selector-class">.name</span></span>

- List the metal layers on which the I/O pins of the block reside

-

``` dbGet top.terms.pins.allShapes.layer.name ``` ``` - 获得所有 spare instances - `````` dbGet [dbGet -p top.insts.isSpareGate 1].name ``` ``` - get 特定instance的pg pin - `````` dbGet [dbGet top.insts.name $instName -p ].pgInstTerms.name ``` ``` **Cadence提供了更为详细的命令,参考如下:**You can use the following single-line dbGet scripts to explore various aspects of your design: - **List all unplaced instances in the design** - `````` dbGet [dbGet -p top.insts.pStatus unplaced].name ``` ``` - **List all placed instances in the design** - `````` dbGet [dbGet -p top.insts.pStatus placed].name ``` ``` - **List all fixed instances in the design** - `````` dbGet [dbGet -p top.insts.pStatus fixed].name ``` ``` - **List the metal layers on which the I/O pins of the block reside** - `````` dbGet top.terms.pins.allShapes.layer.name ``` ``` - **List the non default rules (NDR) in the design** - `````` dbGet head.rules.name ``` ``` - **List the NDRs applied on a specified net** - `````` dbGet [dbGet -p top.nets.name netName].rule.name ``` ``` - **List net names with specific max or min voltage** - - `````` dbGet [dbGet top.nets.maxVoltage value –p].name `````` dbGet [dbGet top.nets.minVoltage value –p].name ``` ``` - **Get the placement status of an instance** - `````` dbGet [dbGetInstByName instName].pStatus ``` ``` - **To avoid splitting of a specified multibit flop, during multibit Optimization** - `````` dbSet [dbGetInstByName] .dontSplitMultibit 1 ``` ``` - **To avoid merging of a specified multibit flop, during multibit Optimization** - `````` dbSet [dbGetInstByName] .dontMergeMultibit 1 ``` ``` - **Get the coordinates of a rectangular routing blockage** - `````` dbGet top.fplan.rBlkgs.shapes.rect ``` ``` - **Get the coordinates of a rectilinear routing blockage** - `````` dbGet top.fplan.rBlkgs.shapes.poly ``` ``` - **List all cell types used in the design** - `````` dbGet -u top.insts.cell.name ``` ``` **Note:** The "-u" parameter filters out the duplicate objects. - **Get the size of block placement halos** - - - - `````` dbGet [dbGet -p2 top.insts.cell.subClass block*].pHaloTop `````` dbGet [dbGet -p2 top.insts.cell.subClass block*].pHaloBot `````` dbGet [dbGet -p2 top.insts.cell.subClass block*].pHaloLeft `````` dbGet [dbGet -p2 top.insts.cell.subClass block*].pHaloRight ``` ``` - **Get the size and top/bottom layers of block routing halos** - - - `````` dbGet [dbGet -p2 top.insts.cell.subClass block*].rHaloSideSize `````` dbGet [dbGet -p2 top.insts.cell.subClass block*].rHaloBotLayer.name `````` dbGet [dbGet -p2 top.insts.cell.subClass block*].rHaloTopLayer.name ``` ``` - **Ensure all your tiehi/tielo connections have tie cells (and are not connected to a rail instead)** - - - - - `````` dbGet top.insts.instTerms.isTieHi 1 `````` dbGet top.insts.instTerms.isTieLo 1 `````` The previous commands should return "0x0" if all connections have tie cells. If "1s" are returned, use the following commands to find the terms that still need a tie cell: `````` dbGet [dbGet -p top.insts.instTerms.isTieHi 1].name `````` dbGet [dbGet -p top.insts.instTerms.isTieLo 1].name ``` ``` - **Get all instTerm names that are tied to tieLo cells** - `````` dbGet [dbGet -p [dbGet -p2 top.insts.cell.subClass coreTieLo].instTerms.net.allTerms.isInput 1].name ``` ``` - **Change the routing status of a net (for example, from FIXED to ROUTED)** - `````` dbSet [dbGet -p top.nets.name netName].wires.status route ``` ``` - **Get the status of the design** - - - - - - `````` dbGet top.statusIoPlaced `````` dbGet top.statusPlaced `````` dbGet top.statusClockSynthesized `````` dbGet top.statusRouted `````` dbGet top.statusRCExtracted `````` dbGet top.statusPowerAnalyzed ``` ``` - **List the layers used in a net** - `````` dbGet [dbGet -p top.nets.name netName].wires.layer.name ``` ``` - **Selecting Shield Nets of a net** - `````` dbSelectObj [dbget [dbget -p [dbGet -p top.nets.name $net].shieldNets.name GND].sWires.shieldNet.name $net -p2] ``` ``` NOTE: $net is the net for which you want to select the shield. - **Find all instances of a certain cell type** - `````` dbGet [dbGet -p2 top.insts.cell.name cellName].name ``` ``` - **Determine the size of a cell in the library, but not necessarily in the current design** - `````` dbGet [dbGetCellByName cellName].size ``` ``` - **List the nets marked in the db as clock net** - `````` dbGet [dbGet -p top.nets.isClock 1].name ``` ``` **Note:** Before running the previous command, build a timing graph using the timeDesign command. - **Set all instances with a particular pattern in the name to fixed status** - `````` dbSet [dbGet –p top.insts.name *clk*].pStatus fixed ``` ``` - **Get top and bottom routing layers for a route\_type** - - `````` dbGet [dbGet -p head.routeTypes.name routeTypeName].topPreferredLayer.num `````` dbGet [dbGet -p head.routeTypes.name routeTypeName].bottomPreferredLayer.num ``` ``` - **Get database units** - `````` dbGet head.dbUnits ``` ``` - **Get the manufacturing grid** - `````` dbGet head.mfgGrid ``` ``` - **Get physical only cells such as filler cell, end cap cell, and so on** - `````` dbGet [dbGet -p top.insts.isPhysOnly 1].name ``` ``` - **Report Dont Touch instances:** - `````` dbGet [dbGet -p top.insts.dontTouch true].name ``` ``` - **Report Dont Use cells in the database** - `````` dbGet [dbGet -p head.libCells.dontUse 1].name ``` ``` - **Report JTag elements:** - `````` dbGet [dbGet -p top.insts.isJtagElem 1].name ``` ``` - **Report spare instances:** - `````` dbGet [dbGet -p top.insts.isSpareGate 1].name ``` ``` - **Filter all PG pins with direction bidi of a specific instance** - `````` dbGet [dbGet -p [dbGet -p top.insts.name instName].pgCellTerms.inOutDir bidi].name ``` ``` - **Get PG pins connections of a specific instance** - - - - - - `````` proc getInstPGConnect {c} { `````` set inst [dbget -p top.insts.name $c] `````` puts "PG connection of instance $c:" `````` foreach PGT [dbget $inst.pgCellTerms.name] { `````` puts "\tPin : $PGT --> Net: [dbget [dbPGTermNet [dbGetPGTermByName $inst $PGT]].name]" } `````` } ``` ``` - **Get class and subClass of a cell** - - `````` dbGet [dbGetCellByName cellName].baseClass `````` dbGet [dbGetCellByName cellName].subClass ``` ``` - **Selecting all Macros/Blocks of a particular module (or Hierarchical instance)** - `````` selectInst [dbGet [dbGet top.hInst.allTreeInsts.cell.baseClass block -p2].name specify_module_name> ] ``` ``` - **Get all the sequential cells of a particular module** - - `````` selectModule module_name> `````` dbGet [dbGet selected.insts.cell.isSequential 1 -p2].name ``` ``` - **Get the instname / cellname of the driver driving a specific net** - - - `````` set netName netName `````` set inst [dbGet [dbGet -p [dbGet -p top.nets.name $netName].allTerms.isOutput 1].inst] `````` Puts "Net: $netName, driving inst name: [dbGet $inst.name], driving cell name: [dbGet $inst.cell.name]" ``` ``` - **List all layers for the pin of a cell** - `````` dbGet [dbGet -p selected.cell.terms.name pinName].pins.allShapes.layer.extName ``` ``` - **Report points of the polygon that forms the die area** - `````` dbShape -output polygon ``` ``` - **Get Verilog module ports** - `````` dbGet [ dbGet -p1 top.hInst.allTreeInsts.name $moduleInstName].hInstTerms.hTerm.name ``` ``` - **To query top level term pin coordinates and layer number** - - `````` lindex [dbGet [dbGet top.hinst.hinstTerms.term.name- p] .pins.allShapes.shapes.rect] 0 `````` dbGet [dbGet top.hinst.hinstTerms.term.name-p] .pins.allShapes.layer.num ``` ``` - **Query max\_cap for a list of cells** - - `````` cellPtrList [dbGet -p head.allCells.n ame BUF*] `````` foreach cellPtr $cellPtrList {puts "[dbGet $cellPtr.name] [dbFTermMaxCap [dbGet -p $cellPtr.terms.name termName] 1]"} ``` ``` - **Find all instances with a specify property name "myProp" (string property type) and value "xyzzy"** - - `````` set inst_ptrs [dbGet -p top.insts.props {.name == "myProp" && .value == "xyzzy"] `````` Puts "Instances with property myProp and value xyzzy: [dbGet $inst_ptrs.name]" ``` ``` - **Find non-clock ports in a design** - `````` dbGet [dbGet -p [dbGet -p2 top.terms.net.isClock 0].isInput 1].name ``` ``` - **To get information on all tech sites in the design** - - - `````` dbGet head.sites.name `````` dbGet head.sites.size `````` dbIsTechSiteVDDOnBottom [dbGet head.sites.name-p] ``` ``` - **Identify and report ‘physical only’ types of cells (well tap, tie hi/lo, filler, endcap/decap)** You can query the subclass for a cell to check whether it is welltap, tiehigh, tielow or end cap: - - - - - - - - - - - `````` dbGet [dbGet -p head.libCells.subClass].name `````` For example, to get names of well tap cells (specified as ‘CLASS CORE WELLTAP ‘ in LEF), you can use the following command: `````` dbGet [dbGet -p head.libCells.subClass coreWellTap].name `````` Similarly, to get names of tie high / tie low cells (specified as ‘CLASS CORE TIEHIGH’ or ‘CLASS CORE TIELOW’ in LEF), use the following command: `````` dbGet [dbGet -p head.libCells.subClass coreTieHigh].name `````` OR `````` dbGet [dbGet -p head.libCells.subClass coreTieLow].name `````` To report endcap cells (specified as ‘CLASS ENDCAP’ in LEF), use the following command: `````` dbGet [dbGet -p head.libCells.subclass coreEndCap*].name `````` Similarly, to query filler cells with ‘CLASS CORE SPACER’ in the LEF syntax, you can use the following command (similar to other physical-only cells): `````` dbGet [dbGet -p head.libCells.subClass coreSpacer].name ``` ``` - **Print all module names in the design** - - - `````` foreach module_name [dbGet top.hInst.treeHInsts.cell.name] { `````` Puts "$module_name" `````` } ``` ``` This will not include the top module name. To get the top module name, run the following command: - `````` dbGet top.name ``` ``` - **Get all leaf cells used in the design** - - - `````` foreach leaf_name [dbGet -u top.insts.cell.name] { `````` Puts "$leaf_name" `````` } ``` ``` - **Apply set\_dont\_touch on selected instances** Select the instances on which to apply set\_dont\_touch. For example, select all level-shifter instances with the "LS" prefix: - - - - - `````` dbGet top.insts.name LS* `````` Then, run the following command: `````` foreach term [dbGet selected.instTerms.net.term –e] { `````` set_dont_touch [dbGet $term.net.name] true `````` } ``` ``` - **Skip routes hierarchical hard macro nets** - - - - - - `````` proc skiproutesOnHmsNets {hmInstPattern} { `````` deselectAll `````` selectInst *$hmInstPattern* `````` dbset selected.hinst.hnets.net.skipRouting 1 `````` deselectAll `````` } ``` ``` - **Removing nets over the Macros along with pitches and vias** Incase some nets are routed over the Hard Macros, you can remove such nets along with pitches and vias using following command: - - - - - - `````` foreach c [dbGet [dbGet -p2 top.insts.cell.baseClass block].name] { `````` set j [dbGet -p top.insts.name $c ] `````` dbSelectObj [dbQuery -area [dbGet $j.box ] -objType regular] `````` puts "Deleting object at [dbGet $j.box ] within Block [dbget $j.name]" `````` editDelete -selected -type Signal -use SIGNAL `````` } ``` ``` - **Get the number of vias that are not power in a routed design** - `````` llength [dbGet [dbGet -p top.nets.isPwrOrGnd 0].vias] ``` ``` - **Break the DFM flow if metal fills are not added to design using run\_pvs\_metal\_fill.** Include following set of command to break the script if metal fill is not added to design puts "Checking if run\_pvs\_metal\_fill successfully inserted metal fill shapes..." - - - - - - - - - - `````` if {[dbGet [dbGet -p top.nets.name _FILLS_RESERVED].sWires.shape fillwire] >= 0} { `````` puts "db has metal fill - continuing..." `````` set has_fill 1 `````` } else { `````` puts "db has no metal fill - stopping dfm run..." `````` set has_fill 0 `````` } `````` if {$has_fill 1} { `````` break `````` } else { .. ``` ``` - **Report instance pin shape mask** You can use TCL procedure below to report the mask(color) of the instance pin: - - - - - - - - `````` proc pinColor {instPin layer} { `````` if {![regexp $layer [dbGet [dbGet top.insts.instTerms.name $instPin -p].cellTerm.pins.allShapes.layer.name]]} { `````` Puts "$instPin doesn't have pin shape on $layer" `````` } else { `````` dbGet [dbGet [dbGet top.insts.instTerms.name $instPin -p].cellTerm.pins.allShapes.layer.name $layer -p2].shapes.mask `````` } `````` } `````` pinColor Ainst/o VIA1 ``` ``` - **Report latency of all memories in the design** Following script prints the latency of all memories with cell name \*RAM\* and clock pin name \*CLK. You can change \*RAM\* with cell name of the desired memories, or as per your design. - - - - `````` set mem_pin [dbget [dbget top.insts.cell.name *RAM* -p2].instTerms.name *CLK] `````` foreach i $mem_pin { `````` puts "$i [get_property [get_pins $i] actual_latency_late_rise_max]" `````` } ``` ``` - **Report all flop instances with reset pin connected to the supply** - - - - - - - - - - - - - - - - - - - - - - - - `````` # dentify all flops with reset tied directly to the vss rail `````` # report total count, and each instname and cellname to an `````` # output file named 'flop_with_tied_rst.rpt' `````` proc findRstPinsTiedToRail{ $VSS_name $RSTport } { `````` # don't echo dbGet, etc. to screen/log: `````` setPreference CmdLogMode 1 `````` # output file name: `````` set ofile "flop_with_tied_rst.rpt" `````` set ecofp [ open $ofile w ] `````` set cnt [llength [dbGet [dbGet [dbGet top.nets.name $VSS_name -p].instTerms.cellTerm.name $RSTport -p2 ].inst.name ]] `````` set insts [dbGet [dbGet [dbGet top.nets.name $VSS_name -p].instTerms.cellTerm.name $RSTport -p2 ].inst ] `````` set cnt2 [llength $insts] `````` puts $ecofp "Total: $cnt $cnt2" `````` #foreach inst_ptr [dbGet [dbGet [dbGet top.nets.name $VSS_name -p].instTerms.cellTerm.name $RSTport -p2 ].inst ] `````` foreach inst_ptr $insts { `````` set inst_name [dbGet $inst_ptr.name] `````` set cell_ptr [dbInstCell $inst_ptr] `````` set cell_name [dbGet $cell_ptr.name] `````` set rst_port [dbGet $inst_ptr.instTerms.cellTerm.name $RSTport -p2] `````` set net [dbGet $rst_port.net.name] `````` puts $ecofp "$inst_name $cell_name " `````` } `````` close $ecofp `````` } ``` ``` To get the status of a design: - - - - - - - - - - - - `````` dbGet top.?? status* // reports the list of status at particular stage `````` statusClockSynthesized: 0 `````` statusGRouted: 0 `````` statusIoPlaced: 1 `````` statusPlaced: 1 `````` statusPowerAnalyzed: 0 `````` statusRCExtracted: 0 `````` statusRouted: 1 `````` statusScanOpted: 0 `````` Example to check a particular value: `````` dbGet top.statusPlaced `````` 1 // it shows design is placed ``` ``` **Note:** The top.statusClockSynthesized flag is only for FE-CTS \[setCTSMode -engine ck\] not for CCOpt. - **Create SDP(structured data path) groups of clock gates and flops:** The following script will find the clock gates and the flops connected to the clk pin in the design and group them together using createSdpGroup **Script:** - - - - - - - `````` set clock_gates [dbget [dbget top.insts.cell.name *cgc* -p2].instTerms.name *clk -p2] `````` foreach i $clock_gates { `````` ## find clock net of the clock gate `````` set clock_net [dbget $i.instTerms.name *clk -p] `````` set sdp_group_name [string map {/ _} [join [dbget $i.name] ""]] `````` set flops [dbget [dbget $clock_net.net.instTerms.isInput 1 -p].inst.name ] `````` createSdpGroup -name $sdp_group_name -alignByPinName clk -inst $flops ``` ``` } **Note:** Please use cell name and clock pins name(cgc and clk used for example) as per the library specifications. 转载:全栈芯片工程师

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

点赞

收藏

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:3425次2024-01-17 11:25:11

-

浏览量:2920次2023-10-12 14:39:21

-

浏览量:4671次2020-03-03 22:19:33

-

浏览量:4016次2017-11-23 18:51:47

-

浏览量:4916次2017-10-23 19:20:34

-

浏览量:5761次2022-03-02 09:00:10

-

浏览量:2575次2020-08-14 18:20:33

-

浏览量:1242次2023-05-16 10:55:38

-

浏览量:3914次2022-05-26 10:04:36

-

浏览量:12934次2022-07-13 22:34:27

-

浏览量:2254次2020-08-07 16:54:02

-

浏览量:1472次2023-07-27 10:37:40

-

浏览量:2549次2019-12-03 16:19:11

-

浏览量:2317次2019-12-03 16:21:12

-

浏览量:2446次2020-09-15 09:35:02

-

浏览量:3175次2020-09-04 13:47:44

-

浏览量:2396次2023-08-19 14:25:08

-

浏览量:2660次2017-11-17 14:46:14

-

浏览量:1538次2023-04-19 09:11:57

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

david

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友