技术专栏

Xilinx Adapt 技术大会中国站,来了!

Xilinx Adapt 2021是赛灵思举行的线上技术盛会,云集了赛灵思高层和技术专家,以及众多合作伙伴与客户,共同探讨和分享最新技术方案、用户案例、产品培训和应用实操,助您发掘“自适应计算”的价值,打造适合自己的应用解决方案。

Xilinx Adapt 2021是赛灵思举行的线上技术盛会,云集了赛灵思高层和技术专家,以及众多合作伙伴与客户,共同探讨和分享最新技术方案、用户案例、产品培训和应用实操,助您发掘“自适应计算”的价值,打造适合自己的应用解决方案。

2021 年 11 月 16 日至 12 月 14 日,Xilinx Adapt – 中国站即将于线上举行。作为 Xilinx Adapt 2021 的延申,Xilinx Adapt – 中国站将持续 5 周,并针对本土市场带来一系列量身打造的特色内容。

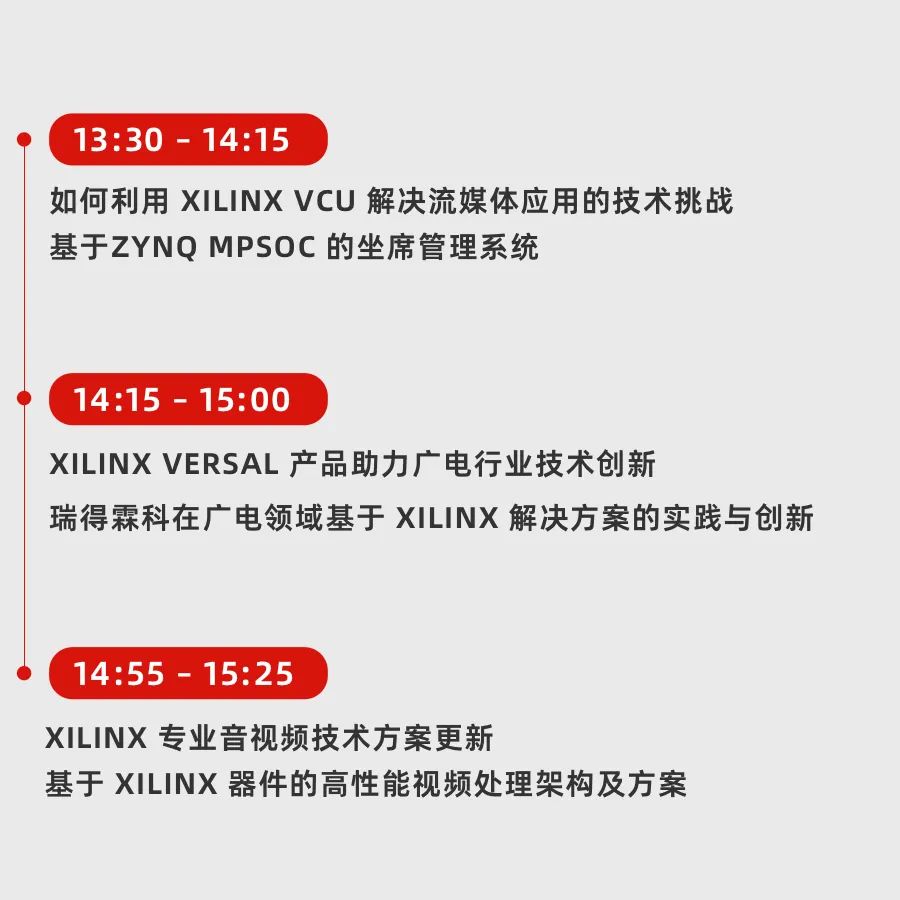

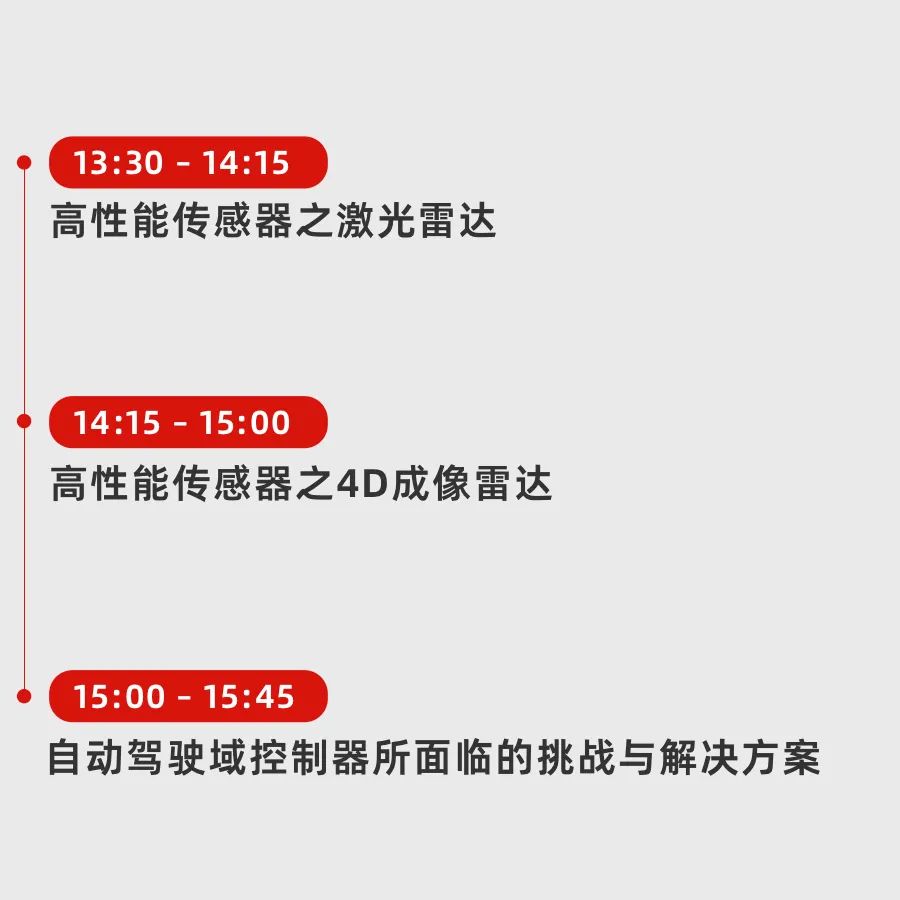

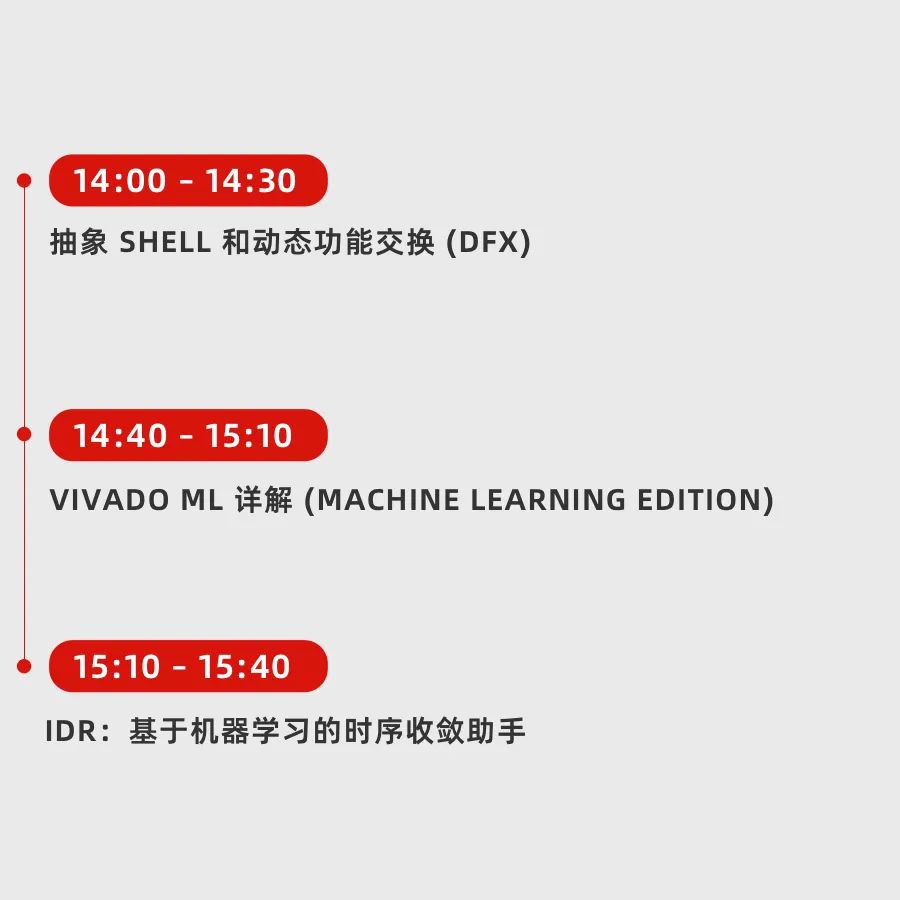

点击下方图片,查看全中文分论坛日程安排

点击下方图片,查看全中文分论坛日程安排

分享嘉宾(持续更新)

分享嘉宾(持续更新)

Xilinx Adapt – 中国站邀请了众多赛灵思本地专家与合作伙伴,带来不同应用领域的解决方案解读和案例分享。

邀请好友有好礼

邀请好友有好礼

报名成功后,可根据赛灵思官微提示,生成自己的专属海报。通过您的专属海报邀请好友,排名前100位者均可获得互动礼品。

点击下方活动专区**,快来报名吧!**

Xilinx Adapt - 中国站

Xilinx 赛灵思官微

扫描二维码 | 关注我们

您的“在看”,是Xilinx进步的动力!

转载:赛灵思

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

点赞

收藏

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:3233次2022-01-10 09:00:20

-

浏览量:2401次2022-01-17 09:01:39

-

浏览量:2715次2022-01-12 09:00:26

-

浏览量:2995次2022-01-09 09:00:19

-

浏览量:3485次2022-01-11 09:00:22

-

浏览量:2360次2022-01-14 09:00:21

-

浏览量:2215次2022-01-13 09:00:57

-

浏览量:2671次2022-01-15 09:00:26

-

浏览量:2486次2021-12-31 09:00:34

-

浏览量:2744次2022-01-05 09:00:22

-

浏览量:2616次2019-07-10 13:57:56

-

2022-01-02 09:00:38

-

浏览量:2939次2022-01-18 09:00:18

-

浏览量:2626次2021-12-30 13:59:54

-

浏览量:3348次2022-03-15 09:00:16

-

浏览量:2169次2018-06-28 14:11:25

-

浏览量:2229次2022-01-25 09:00:23

-

浏览量:7975次2022-01-24 09:00:18

-

浏览量:3832次2022-05-31 10:57:34

切换马甲

上一页

下一页

打赏用户

共 0 位

我要创作

分享技术经验,可获取创作收益

分类专栏

-

253篇

热门专栏

- FPGA的设计艺术(21)Verilog中如何对组合逻辑进行建模?

- XDF(美洲站)首站告捷,名企云集,自适应技术全面开花 —— 期待 12 月份亚洲站

- 12G-SDI高清视频开发案例,让4K视频采集更便捷!基于Xilinx MPSoC高性能平台

- FPGA的设计艺术(20)高阻态的正反两用?

- 敲黑板!Xilinx Adapt中国站参会须知

- FPGA硬件算法(1)长江后浪推前浪之流水线

- FPGA的设计艺术(12)使用parameter构建可重用的逻辑设计

- FPGA的设计艺术(14)使用函数和任务提升逻辑的可重用性

- 工程师离不开的那些电路设计工具,你用过几个?

- FPGA逻辑设计回顾(2)那些年学习FPGA较为常见的疑问?

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

david

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友