探索高性能 5G 无线方案

这一格局的改变,也意味着 5G 网络需要更加灵活多变和能够适应各个网络细分市场的产品及解决方案来支撑。到底怎样的产品及解决方案最贴合 5G 网络新需求?什么样的技术又能快速聚合运营商网络中不同端口速率、接口、协议和连接标准?对于普遍存在于 5G 网络中各方面的安全问题又将如何破解?

这一格局的改变,也意味着 5G 网络需要更加灵活多变和能够适应各个网络细分市场的产品及解决方案来支撑。到底怎样的产品及解决方案最贴合 5G 网络新需求?什么样的技术又能快速聚合运营商网络中不同端口速率、接口、协议和连接标准?对于普遍存在于 5G 网络中各方面的安全问题又将如何破解?

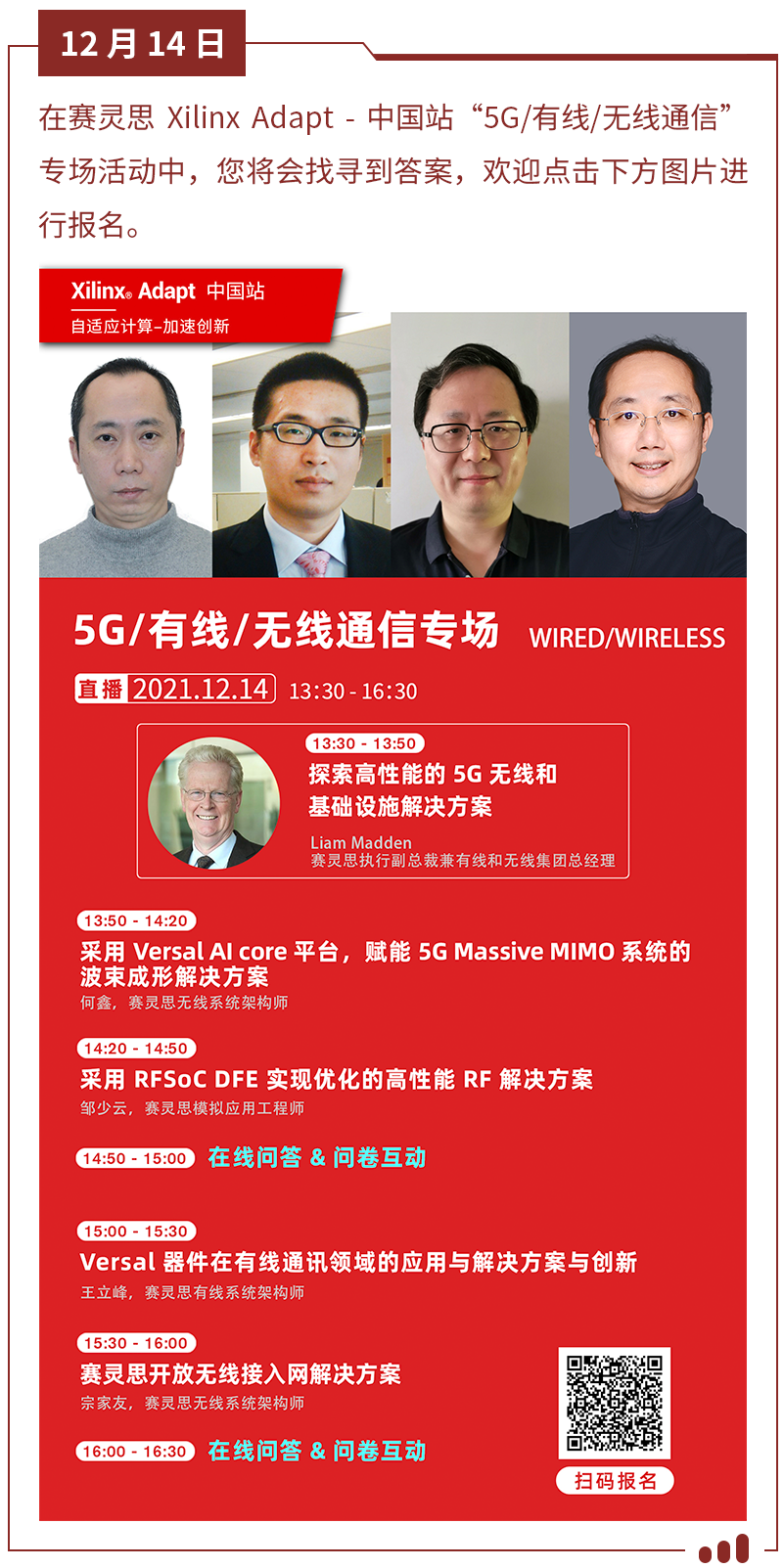

作为 5G 领域扮演积极的参与者和引领者,赛灵思不断加强产品布局,包括 5G O-RAN mMIMO 无线电产品系列、O-DU 的加速器卡、商用芯片 +IP+ 服务。今年 4月,Mavenir与赛灵思宣布携手推出 Open RAN 大规模 MIMO 产品组合,以及全面的一体化软硬件解决方案,打造 5G 王牌解决方案。本次专场活动,赛灵思也将深入地与通信从业者分享 Versal 和 RFSoC 产品在 5G 无线**,**有线通信领域的全新特性以及解决方案,加速 5G 变革。

作为 5G 领域扮演积极的参与者和引领者,赛灵思不断加强产品布局,包括 5G O-RAN mMIMO 无线电产品系列、O-DU 的加速器卡、商用芯片 +IP+ 服务。今年 4月,Mavenir与赛灵思宣布携手推出 Open RAN 大规模 MIMO 产品组合,以及全面的一体化软硬件解决方案,打造 5G 王牌解决方案。本次专场活动,赛灵思也将深入地与通信从业者分享 Versal 和 RFSoC 产品在 5G 无线**,**有线通信领域的全新特性以及解决方案,加速 5G 变革。

除此之外,移动无线接入网正在经历从专有接口到开放式接口的范式转换。随着开放程度的提高,系统集成商和运营商都面临着新挑战:第一项是为真正确保不同供应商的基站和无线电能够在网络中进行正确互操作的高效 O-RAN 合规性测试;第二项则是共存。

尽管基于 CPRI 的设备仍在网络中运行,而且世界上也开始有符合 O-RAN 标准的设备,但运营商确实需要一种经济高效的方式,以在单个前端或链路上实现这两种解决方案的多路复用。需要划重点的是,本次专项讨论会上,赛灵思将联合安捷伦、思科合作展示如何应对这两项挑战,使开放网络成为现实。

安全问题老生常谈,赛灵思却有不一样的解题思路。随着数据吞吐量更大,为了确保数据安全,每一个会话都要被保护。与此同时,光速率如何从 200G 增加到 400G,并最终达到 800G。安全网络需要在不影响带宽的情况下跟上线路速率,因此,这意味着需要数千万个安全会话,所有会话都在一个防火墙设备中进行处理。本次研讨会上,赛灵思将重磅演示 100G IP sec 和 MACsec,确保这些处理是在以保证低确定性时延的方式进行。

5G 的快速发展,正在重塑产业格局。与此同时,5G 与千行百业发生的“化学反应”也在持续发酵,逐渐走向“下半场”,当前 5G 发展面临的巨大任务将要确保 5G 网络能用得好,充分发挥出 5G 的真正价值。

转载:赛灵思

- 分享

- 举报

暂无数据

暂无数据-

浏览量:5980次2020-12-03 14:50:45

-

浏览量:2529次2020-03-12 10:36:28

-

2020-10-23 17:51:34

-

2021-07-30 17:01:26

-

浏览量:4034次2020-12-24 11:41:36

-

浏览量:2425次2018-10-28 20:20:17

-

浏览量:2281次2019-11-19 14:35:35

-

浏览量:4383次2020-06-09 14:50:56

-

浏览量:2210次2023-01-11 12:36:23

-

浏览量:2705次2018-07-15 12:04:13

-

浏览量:2537次2019-01-02 16:57:12

-

浏览量:3072次2018-08-20 09:28:40

-

2020-10-28 09:37:31

-

浏览量:3585次2020-09-23 15:34:57

-

浏览量:2484次2019-06-28 10:24:36

-

浏览量:2741次2018-06-18 11:34:13

-

浏览量:4394次2020-11-28 09:44:19

-

浏览量:3597次2020-11-14 10:01:21

-

浏览量:3542次2022-03-01 09:00:32

-

253篇

- 高速串行总线实践(1)Xilinx Virtex-4 RocketIO的端口和属性

- FPGA的设计艺术(6)STA实战之SmartTime时序约束及分析示例(I)

- 高速串行总线设计基础(九)揭秘SERDES高速面纱之线路均衡与误码检测

- FPGA零基础学习:理解数字信号和模拟信号

- FPGA逻辑设计回顾(12)RAM以及ROM的RTL设计及其验证

- FPGA的设计艺术(15)逻辑设计及仿真利器之各式各样的循环

- FPGA零基础学习:数字电路中的数字表示

- 敲黑板!Xilinx Adapt中国站参会须知

- FPGA逻辑设计回顾(13)RAM以及ROM的IP核定制以及关键参数

- 高速串行总线设计基础(十)常用MGT协议简介以及自定义协议示例

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友