5212

- 收藏

- 点赞

- 分享

- 举报

Hi3531D V200 ,VI4+VI5组合成的BT1120无法采集到数据

悬赏金¥ 10

已结题

【问题描述】

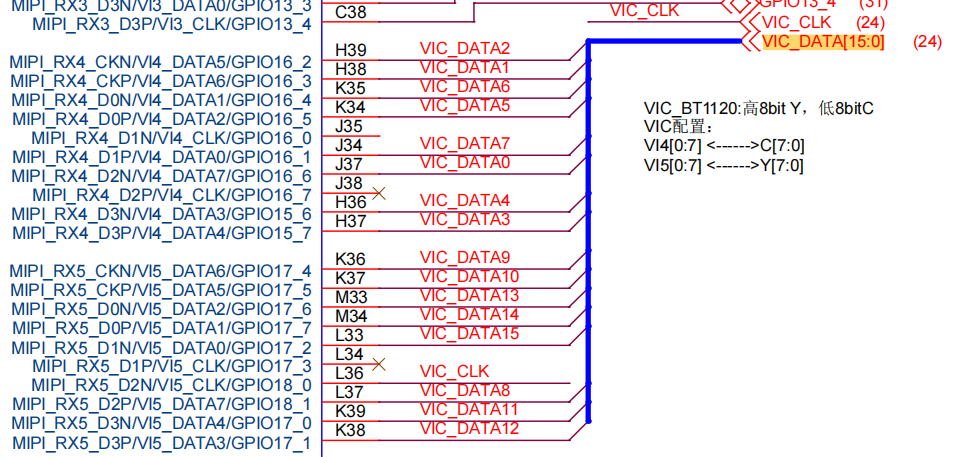

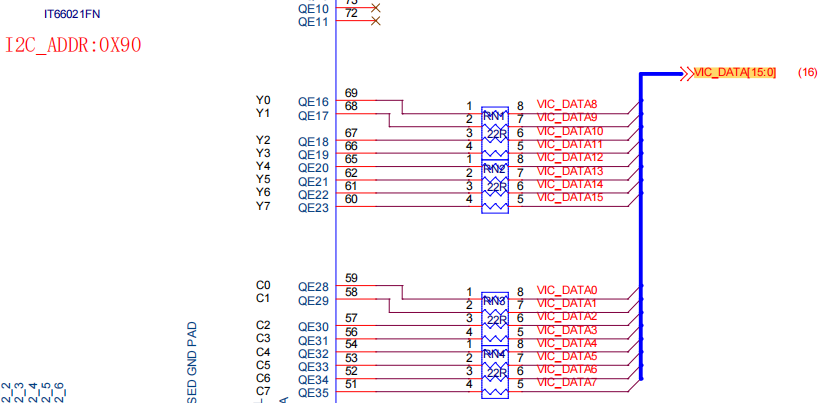

硬件接入VI4_DATA、VI5_DATA做bt1120使用,使用VI5_CLK作为时钟信号,其他的管教复用读配置正确了,VI4上的2组CLK配置成了GPIO,VI5的另一个GPIO也配置成了GPIO

根据《HiMPP 媒体处理软件 V5.0 开发参考.pdf》中“DEV 的选择与 VI 的时钟必须一致”,后面将VI属性设置VI_DEV:5、VI_CHN:20后采集不到中断;前段AD芯片是一颗HDMI转BT1120的芯片,驱动可以确认正常工作。

【所处环境】

HI3531Dv200 + bt1120采集

【尝试解决过程】

1. 将VI_CHN 16 绑定到VI_DEV5 VI无中断;

2. 设置data_reverse VI无中断;

3. 掩码对调设置,VI无中断;

【初步分析】

之前硬件设计一直使用的偶数的设备号,比如VI0+VI1 使用VI0的时钟通道用0 VI4+VI5使用VI4的时钟,使用通道16.这种方式一直可以采集视频。

但是由于硬件走线原因,他参考硬件设计指南里面可以使用奇数设备号的VI_CLK. 目前只能根据文档《HiMPP 媒体处理软件 V5.0 开发参考.pdf》中“DEV 的选择与 VI 的时钟必须一致”,现在按照这个来配置了还是无法采集到视频。麻烦帮忙解决下。

【定位信息】

详见附件:见日志mpp.log . /dev/logmpp下无错误输出

文件: mpp.log

文件: mpp.log

下载

我来回答

回答9个

时间排序

认可量排序

认可0

认可0

或将文件直接拖到这里

悬赏:

E币

网盘

* 网盘链接:

* 提取码:

悬赏:

E币

Markdown 语法

- 加粗**内容**

- 斜体*内容*

- 删除线~~内容~~

- 引用> 引用内容

- 代码`代码`

- 代码块```编程语言↵代码```

- 链接[链接标题](url)

- 无序列表- 内容

- 有序列表1. 内容

- 缩进内容

- 图片

相关问答

-

2019-04-18 18:53:20

-

2017-04-27 10:07:48

-

2022-02-21 18:01:06

-

2016-07-20 11:25:55

-

2017-03-21 10:45:45

-

2017-09-26 15:06:46

-

2017-08-08 16:18:20

-

2021-04-06 13:48:30

-

2017-06-13 14:57:43

-

2016-09-09 12:32:00

-

2023-01-28 14:07:03

-

2018-11-02 14:48:00

-

2019-07-18 08:49:09

-

2019-12-23 11:43:56

-

2018-06-04 18:05:16

-

2018-07-09 13:10:43

-

2018-07-09 14:51:01

-

2012-12-17 10:47:00

-

2016-03-08 14:58:45

无更多相似问答 去提问

点击登录

-- 积分

-- E币

提问

—

收益

—

被采纳

—

我要提问

切换马甲

上一页

下一页

最佳回答

被评为最佳回答,即可获得10元悬赏金额,先回答帮助题主解决问题,会更具优势

悬赏问答

-

10T32crop和fcrop怎么从中间裁剪?

-

53516卡死问题

-

10hi3516cv610 去除风扇声音,人说话声音正常输出不变声

-

5hi3516cv610适配imx662的wdr模式出图图像不正常怎么去解决

-

5ss928 [sample_comm_venc_get_venc_stream_proc]-2627: get venc stream time out, exit thread

-

10要一份RK3576最新硬件资料包

-

5海思DPU的查找表怎么获取

-

10海思Hi3519DV500 自动对焦算法求助

-

10鸿欧派 Hi3519Dv500

-

10【求助】RK3576实现推流和GC2053摄像头颜色偏绿

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

提醒

你的问题还没有最佳答案,是否结题,结题后将扣除20%的悬赏金

取消

确认

提醒

你的问题还没有最佳答案,是否结题,结题后将根据回答情况扣除相应悬赏金(1回答=1E币)

取消

确认

微信扫码分享

微信扫码分享 QQ好友

QQ好友

该回答已被题主采纳为最佳答案

该回答已被题主采纳为最佳答案