FPGA硬件算法(2)矛盾转换之道——Retiming技术

前言

上篇文章:FPGA硬件算法(1)长江后浪推前浪之流水线已经谈了流水线的基础内容。

其实本篇是上一篇的一个补充,上篇内容属于本篇的一部分,它们都可以归入retiming技术之内。

retiming技术是逻辑设计的润滑剂,起到疏通的作用,一起看看吧。

组合逻辑的性能

在常识以及上篇文章中我都都有讲到,组合逻辑的问题是延迟大,组合逻辑的互联也会堆积延迟,大延迟就造成设计性能的下降,造成很多不必要的浪费。

且如果在固定频率的时钟下,使用大量组合逻辑进行运行,即在时序逻辑中,使用了很多组合逻辑的直接互联,会导致时序违规,造成设计失败。

举个例子:

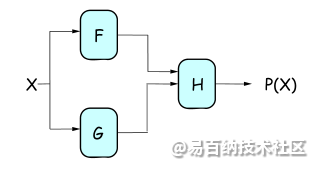

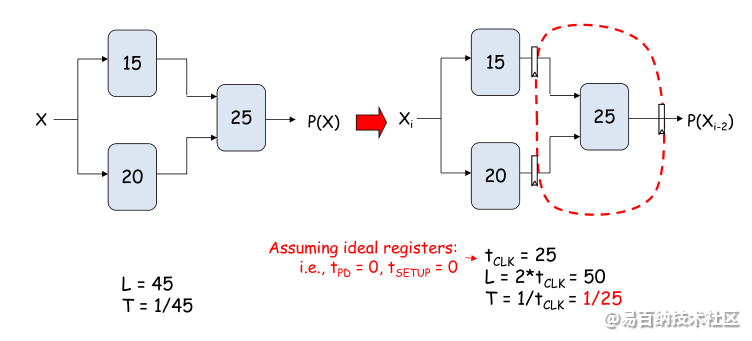

X为输入,P(X)为输出,F/G/H均为组合逻辑块,X经过这几个组合逻辑块的运算后最终输出P(X).

如下图,输入X经过上述组合逻辑块的延迟建模:

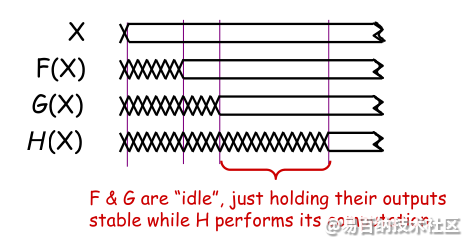

可见,组合逻辑的运算,顺序运行的组合块的延迟会叠加,H在执行运算的时候,F和G都处于空闲状态,造成硬件资源的浪费。

这时我们要提出一个问题:

我们无法更快地获得答案,但我们始终有效地利用我们的硬件吗?

当然可以,转换设计,使用流水线等手段,改善架构,改善时序。

我们可以称这种改善时序的手段为Retiming技术。

Retiming是在系统中移动寄存器的动作。

下面细聊:

Retiming技术

矛盾转换

所谓的矛盾转移就是将一方的主要矛盾转移至另一方,使之变为非主要矛盾。

举个例子:

将一组寄存器从组合逻辑的左边移动到另一边,就可以改善右边时序的压力,但也会增加左边逻辑的压力。

但这么做的前提就是如果一方的压力过大,一方的压力很小,就可以采样这种方式来转移压力。

这里的压力都是指的是时序压力,也即组合逻辑延迟过大的压力。

这样做的好处在于:

- 改善关键路径时序

- 减少中的寄存器数量

如果让这种技术起到上述两种好处,就要合理利用才行。

所谓关键时序路径,就是延迟最大的路径,通过合理的转移寄存器将关键路径切割,改善其时序。

将输入的寄存器移动至输出,还可以起到减少寄存器数量的作用,可以节约资源的使用。

这在我们的实践中可以一点一滴的去体会。

加入流水

以开头话题,组合逻辑的性能为例:

假如从输入到输出的组合逻辑延迟L = 45ns, 则系统内的时钟周期T要大于45ns才能满足需求。

如下图,如果我们在组合逻辑之间加入寄存器呢?

关键路径被截短,为25ns,那么系统时钟周期大于25ns即可。

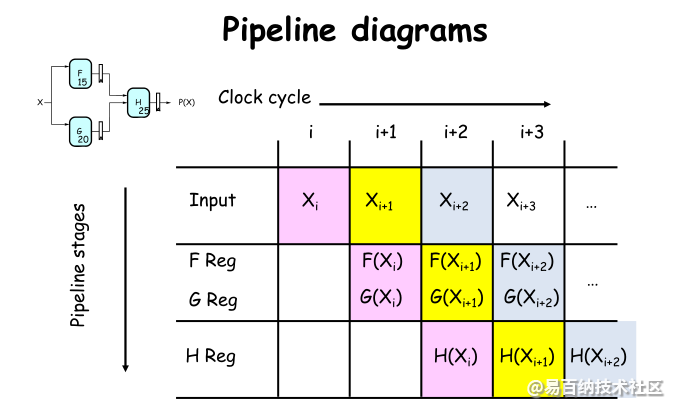

下面我们通过流水图来说明这种设计的工作过程:

横排为时钟周期的方向:i表示时钟周期,i+1表示下一个时钟;

竖排表示流水阶数,通过对角线移动的方式表示每经过一个时钟的特定输入对应的输出。

可见,输入经过2个时钟即可得到最终的计算结果。

流水线的阶数也为2级,称之为2级流水线

下面给出正式的定义:

-

K阶流水线(“k-pipeline”)是一种无循环电路,其在从输入到输出的每个路径上具有恰好k个寄存器。因此,组合电路是0阶流水线。

-

k阶流水线的延迟是所有寄存器通用时钟的k倍。

-

k阶流水线的吞吐量是时钟的频率。

注意:所有寄存器共有的时钟周期必须大于最大组合路径延迟加寄存器的建立时间。

流水线应用好了可以对设计起到润滑的作用,丝滑的设计是好的设设计,如果错误应用,则可能带来意想不到的错误结果,且时序没有得到改善。

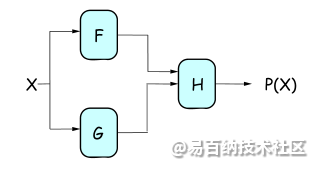

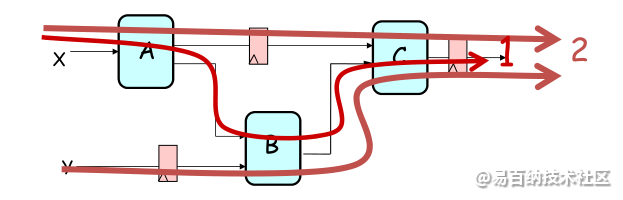

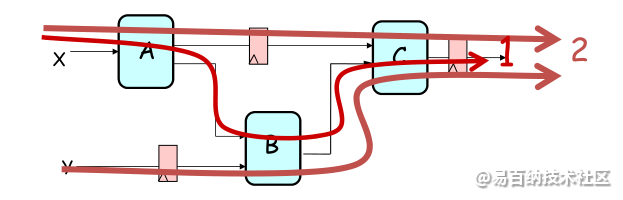

考虑如下设计:

这是几阶流水线结构呢?

着实让人困惑,这是因为从输入到输出的路径上,有的有2个寄存器,有的只有1个。

因此这种情况不要发生在良好设计的流水线中。

如何正确设计流水线?

下面提供一个流程性的方法:

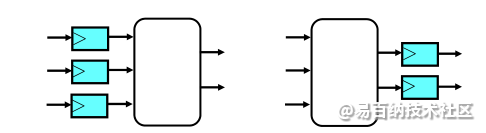

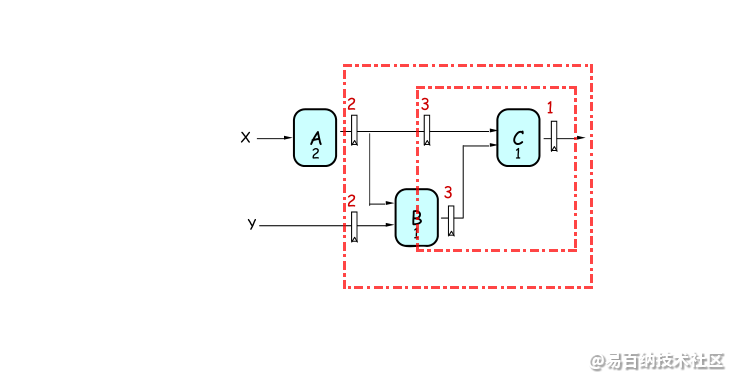

看图总结:

- 在每个输出上添加寄存器。

- 在上一级的每个输出上再增加一个寄存器。绘制一个包括所有新寄存器和部分电路的切割集轮廓。通过将寄存器从所有输出移到切割集的所有输入端来实现Retiming。

- 重复上述步骤

需要添加流水线的地方应该是电路中最慢的路径或者是元件,这是设计的瓶颈,也是主要矛盾。

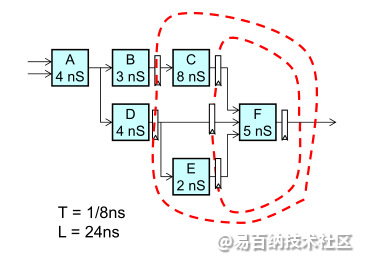

有了这个方式,我们看下之前的问题:

通过上述方式,来将如下流水线设计更改:

更改后:

经验老道的设计师在设计的时候就会避免上述错误的存在,从收入到输出的时序设计是基础也是重中之重。

当然也可以使用上述方式来检验自己的设计,也可以改善原有的设计。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:6037次2021-06-08 22:36:45

-

浏览量:5860次2021-04-11 01:10:40

-

浏览量:8841次2021-02-07 00:59:28

-

浏览量:5069次2021-06-20 20:10:03

-

浏览量:6929次2021-02-14 01:58:16

-

浏览量:6097次2021-03-14 01:12:39

-

浏览量:11332次2020-12-13 19:59:59

-

浏览量:3008次2020-08-19 16:47:34

-

浏览量:714次2026-01-13 15:26:50

-

浏览量:3869次2020-11-20 10:19:03

-

浏览量:20274次2020-12-06 18:59:36

-

浏览量:2151次2025-02-26 21:18:20

-

浏览量:18301次2021-02-19 17:01:32

-

浏览量:3661次2018-05-07 16:22:35

-

浏览量:3388次2021-12-03 17:42:05

-

浏览量:2117次2024-02-18 14:24:39

-

浏览量:4253次2021-08-11 17:04:30

-

浏览量:2219次2022-01-13 09:00:57

-

浏览量:1902次2020-06-19 10:07:41

-

60篇

- FPGA的设计艺术(9)FPGA开发技巧与工程管理

- Maxim推出业界最薄、集成了双路光电检测器的光传感器方案,大幅缩短可穿戴健康及健身产品的上市时间

- XDF(美洲站)首站告捷,名企云集,自适应技术全面开花 —— 期待 12 月份亚洲站

- Xilinx 跻身《财富》 “未来50强”榜单,位列半导体行业之首

- FPGA的设计艺术(26)数据处理的误区之有符号运算的若干问题

- 如何最大限度降低Ćuk稳压器的辐射?这个方法教给你~

- 远程患者监护系统面临的五大设计挑战

- FPGA逻辑设计回顾(9)DDR的前世今生以及演变过程中的技术差异

- 拒绝误报!实例测试这款ADI烟雾探测器!

- 新型大容量嵌入式存储器使用的硅片数量减少了一半

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友