ADS滤波器自动设计(二):低通滤波器的设计

上篇文章为大家简单介绍了自动设计组件的使用方法,这篇文章将为大家具体介绍如何使用ads的自动设计组件设计低通滤波器。

一、最平坦低通滤波器设计

设计指标我们使用我们之前文章中的指标,具体指标如下:

- 最平坦低通滤波器

- 截止频率为1GHz

- 阻抗为75Ω

- 在2GHz时插入损耗至少为30dB

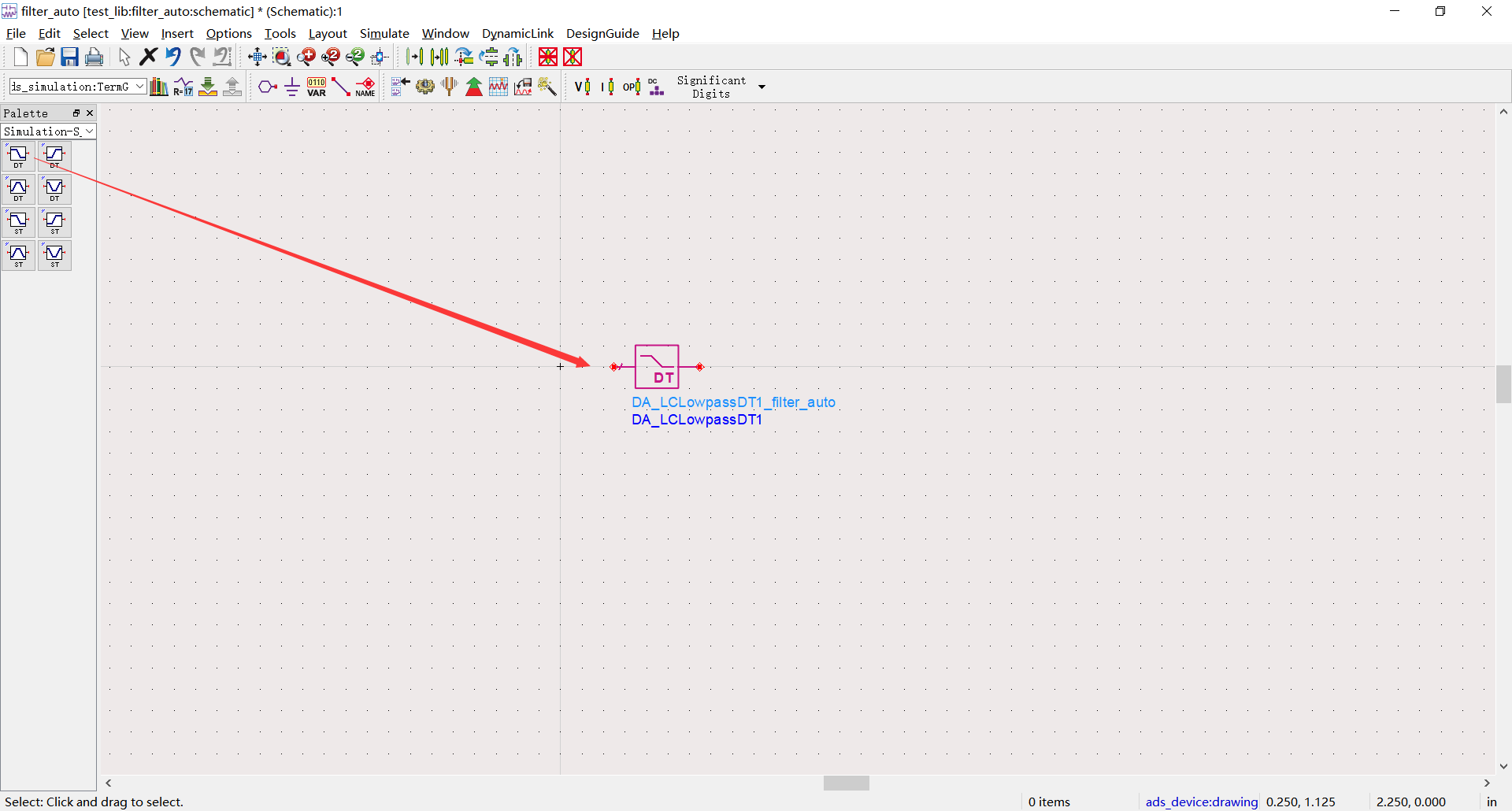

首先打开“Filter DesignGuide”,放置低通滤波器元件,在“Filter DesignGuide”中选择我们放置的滤波器元件。如图:

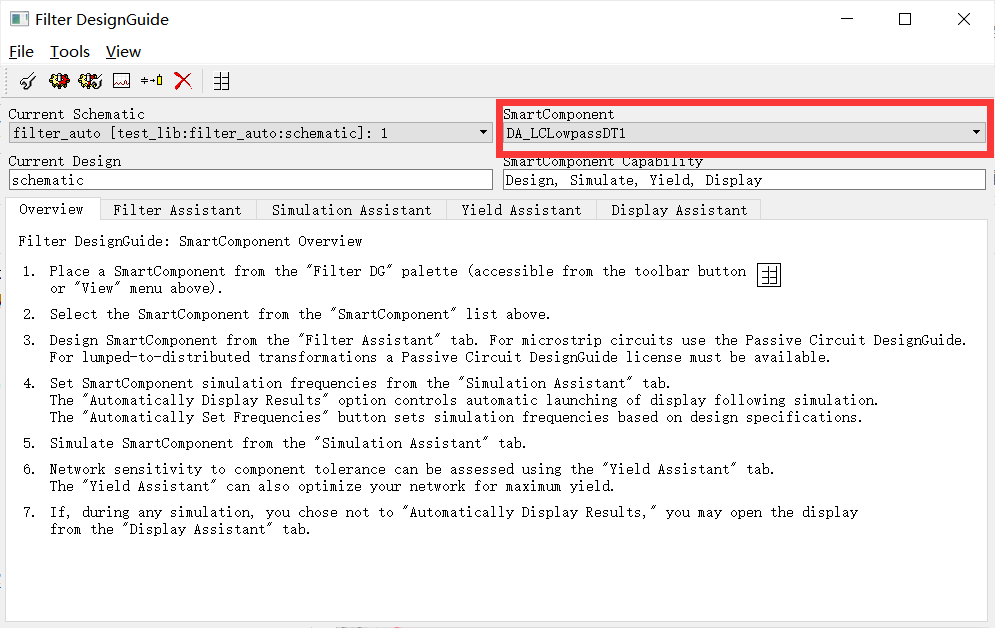

为了方便对比,我们和之前文章中一样,选择第一个元件为并联电容,如图:

阻抗选择为75欧姆,如图:

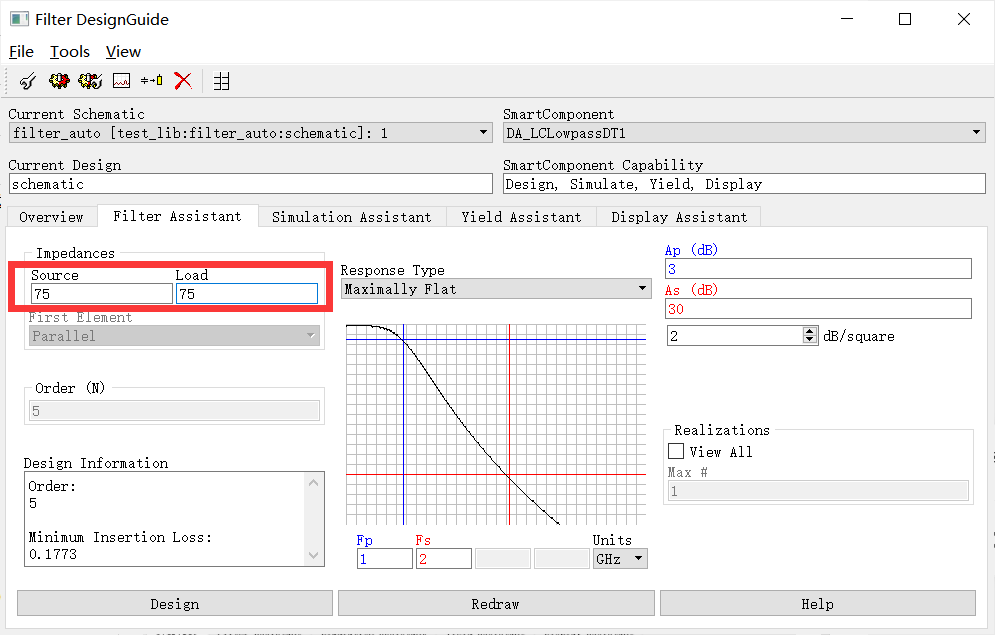

选择滤波器类型,如图:

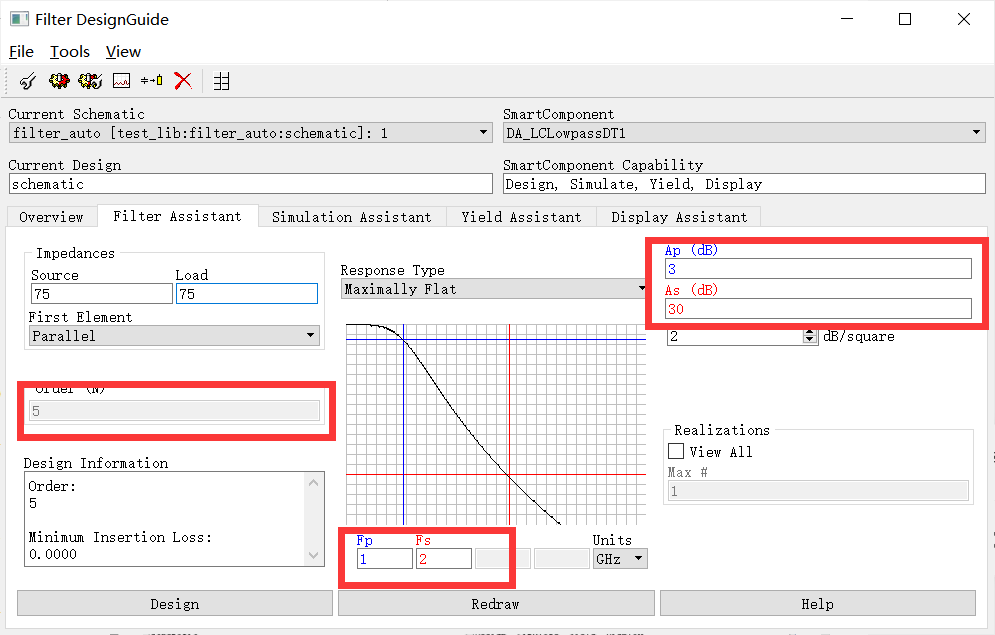

设置截止频率,然后输入2GHz处的损耗要求,确定阶数,如图:

最终确定阶数N=5,接着点击“Design”,完成设计。查看子电路:

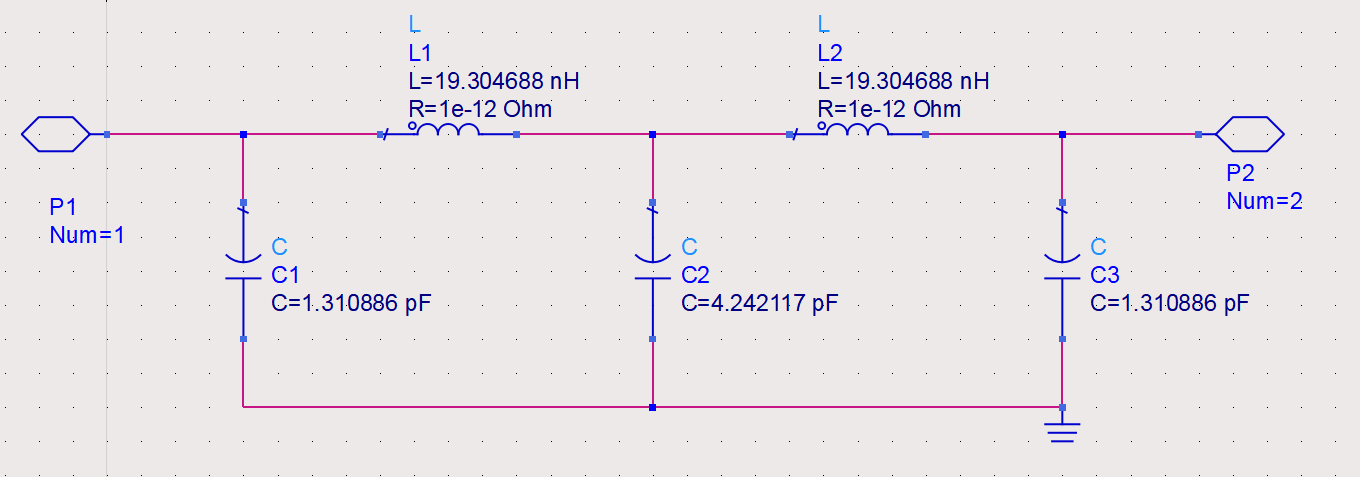

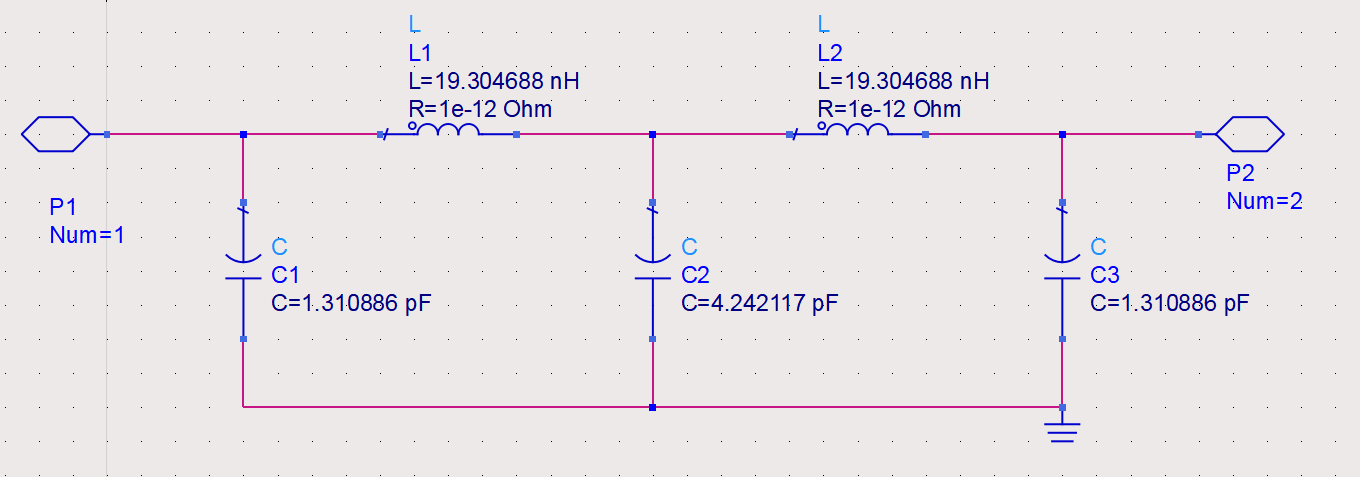

我们可以和之前我们设计的滤波器电路进行对比(上图为之前设计的电路,下图为自动设计的电路):

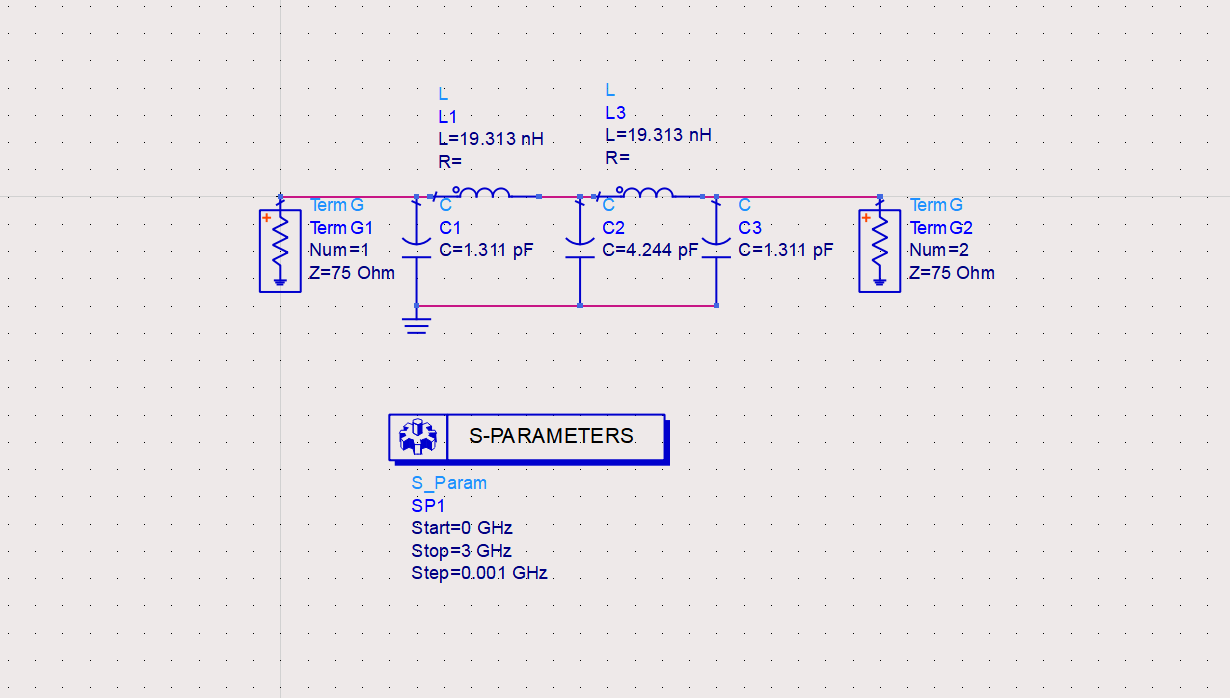

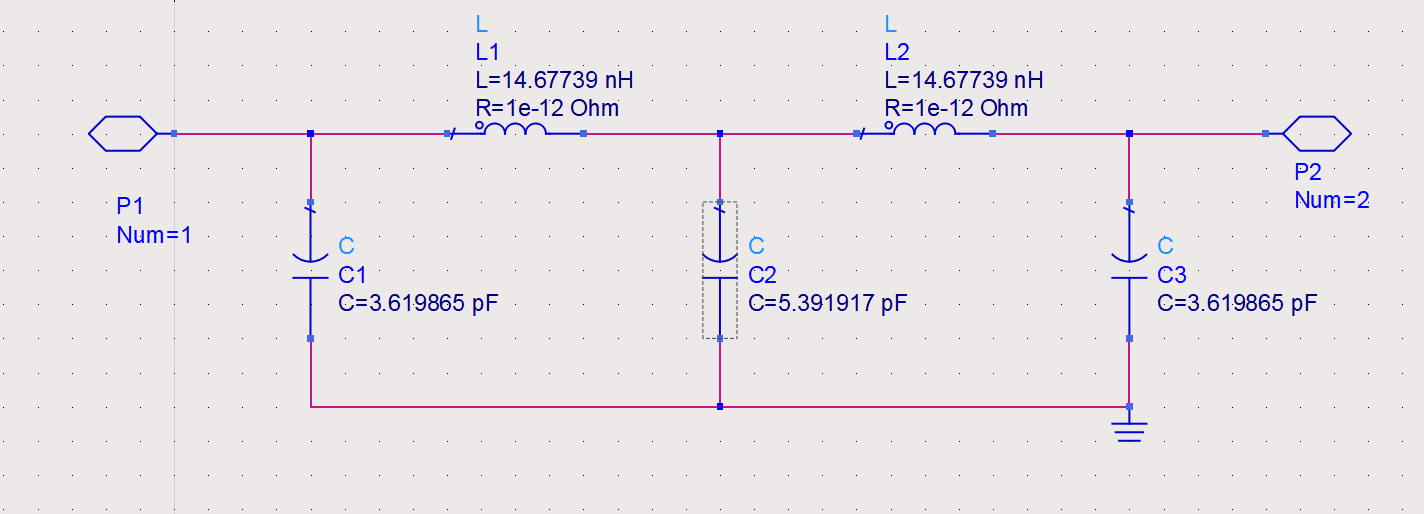

可以看到,两电路几乎完全一样。接下来,我么接入S参数仿真电路,进行仿真,电路如下:

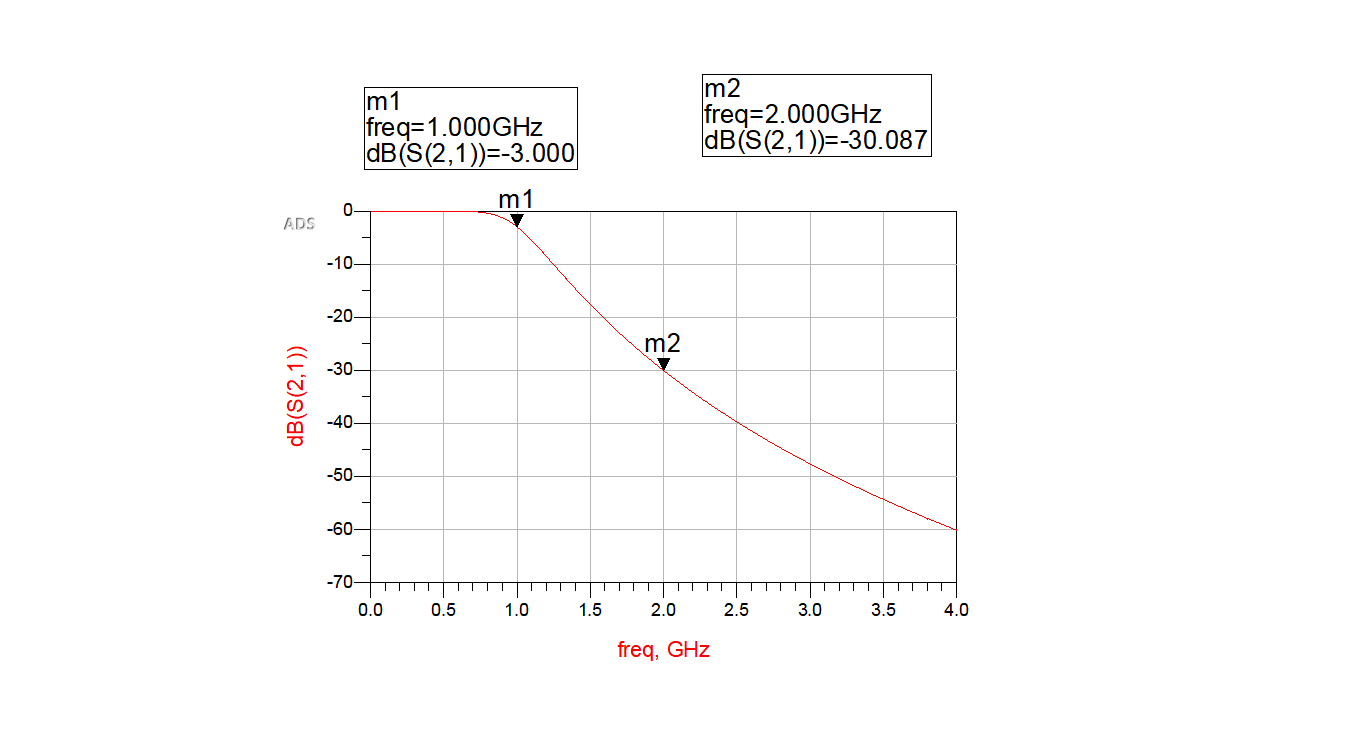

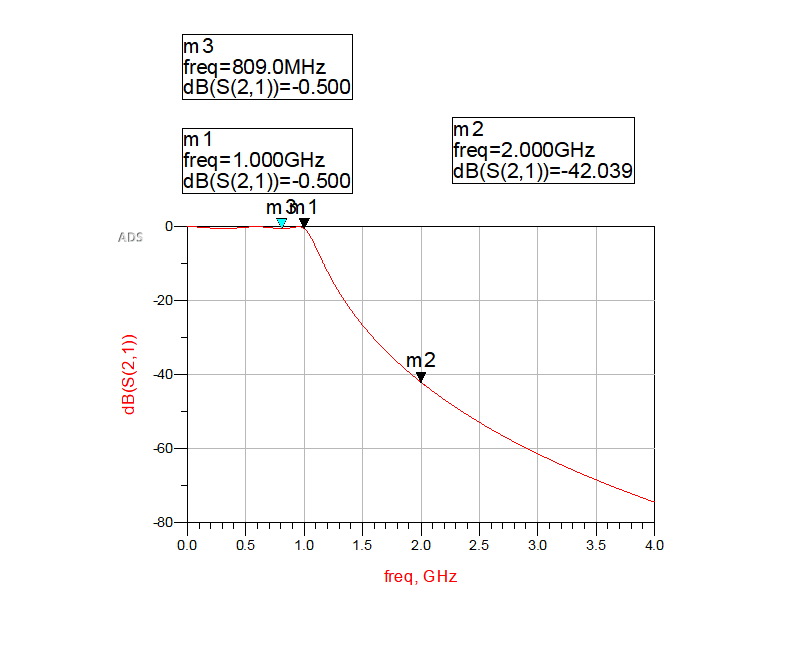

仿真结果如下:

符合设计要求。

二、等波纹低通滤波器设计

依旧采用之前文章中的指标,具体设计指标如下:

- 带内波纹0.5dB

- 截止频率为1GHz

- 阻抗为75Ω

- 在2GHz处插入损耗至少为25dB

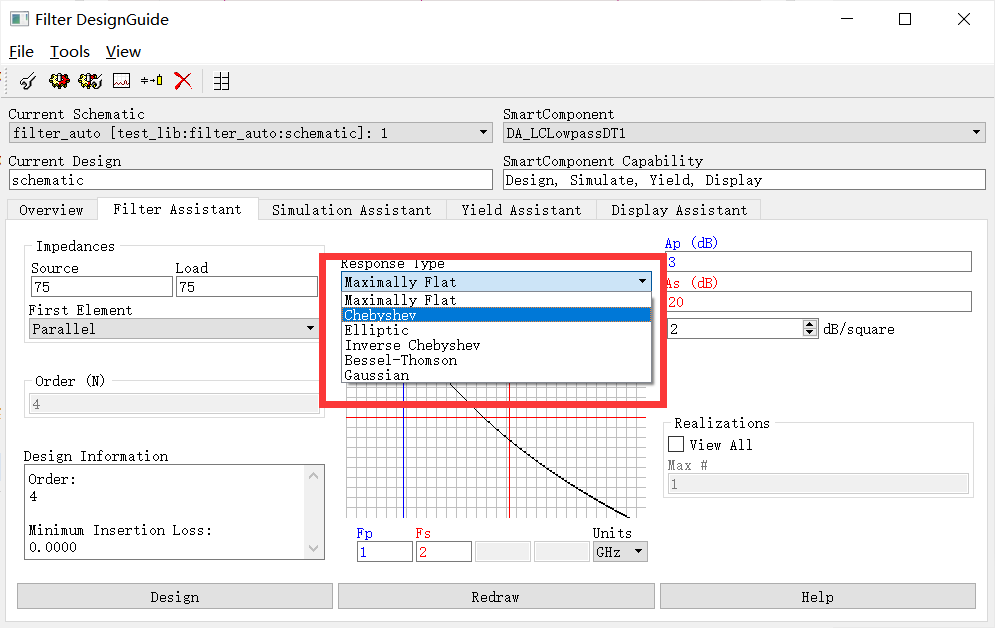

我们直接在最平坦低通滤波器的基础上进行修改,首先确定滤波器类型:

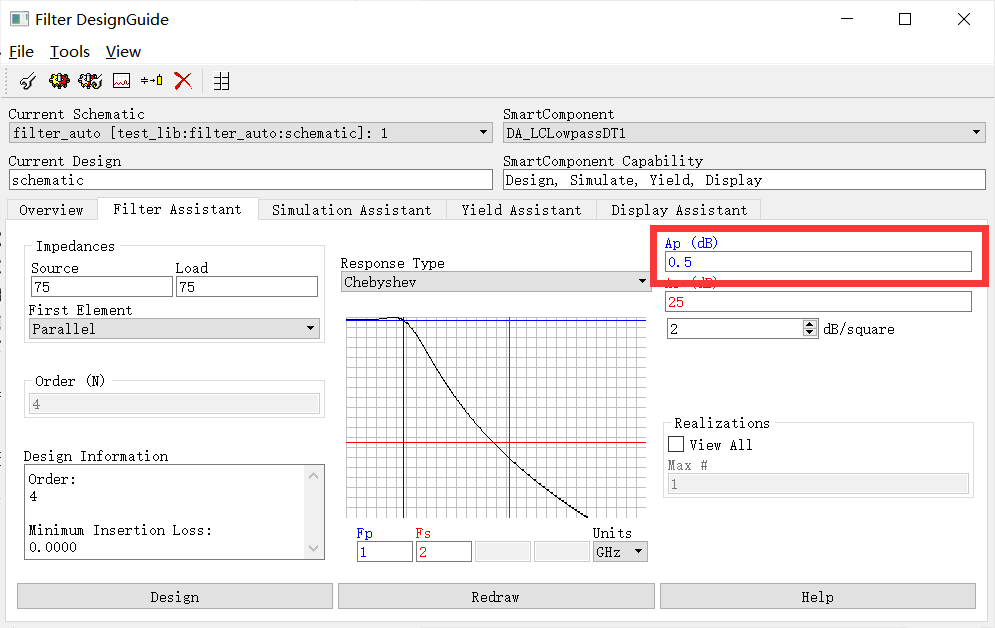

同样第一个元件为并联元件,然后填入设计指标:

需要注意的是,带内波纹为0.5dB幅值时,Ap处的损耗要填写0.5dB,不再是3dB了。若设计的滤波器是3dB等波纹滤波器时,此时Ap才是3dB,其他的设计过程都类似。

可以看到,最终确定的阶数N=4,这和我们之前设计的结果一致。

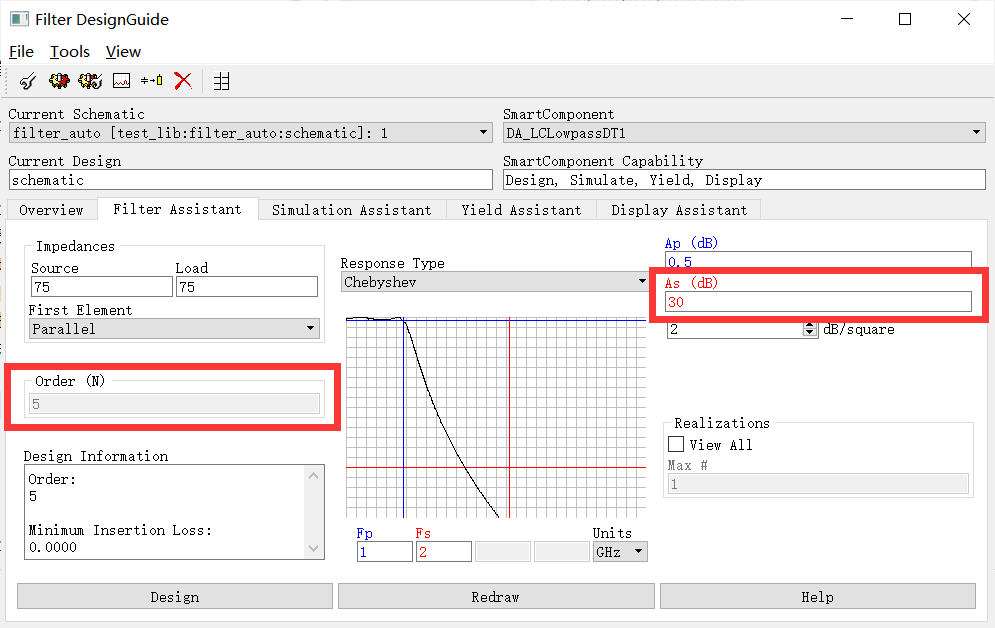

细心的小伙伴已经看出来了,当N为偶数时,负载阻抗不一定等于滤波器的特性阻抗,为了方便,我们可以提高2GHz处插入损耗的值,将滤波器的阶数确定为5。

如图:

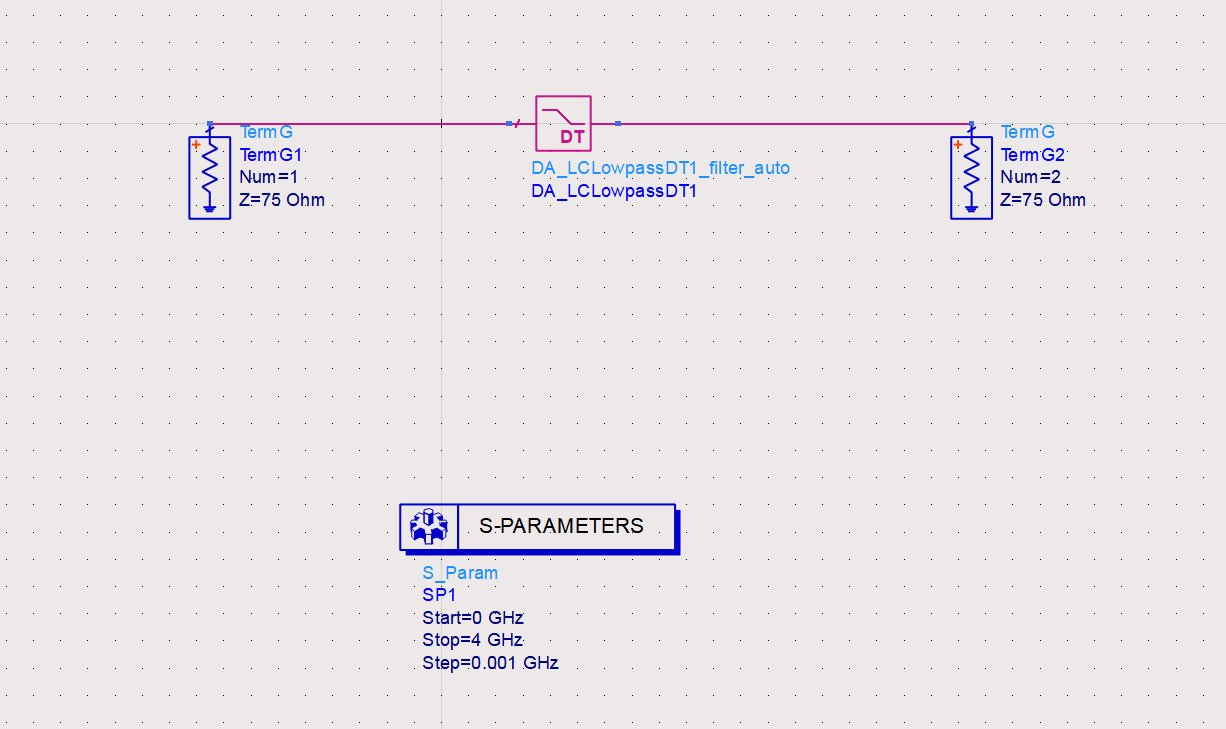

点击“设计”按钮,完成设计,子电路如下:

仿真结果如下:

当我们需要设计一个3dB等波纹的滤波器时,我们只需要修改Ap的值为3dB即可,其他步骤类似,因此,我们不再赘述3dB等波纹滤波器的设计方法。

三、总结

本篇文章为大家介绍了使用ads自动设计组件设计低通滤波器的方法,接下来的文章将继续为大家介绍如何使用ads自动设计组件设计高通滤波器。

- 分享

- 举报

-

小钫 2022-07-08 11:09:14回复 举报为什么我的ads点design没反应?而且通带阻带设置为kHz时,就报错,说:Could not evaluate value without simulation The parameter 'Fp' of the instance DA_LCLowpassDT1 is only allowed to have a constant value. It should not be an expression. 求大佬解答。

-

浏览量:12933次2021-01-29 12:25:06

-

浏览量:25040次2021-01-29 16:50:41

-

浏览量:12960次2021-01-21 11:07:14

-

浏览量:5799次2022-02-13 09:00:13

-

浏览量:13937次2021-01-18 17:28:31

-

浏览量:18925次2021-01-18 13:46:39

-

浏览量:9102次2022-02-14 09:00:16

-

浏览量:7918次2021-01-20 08:36:19

-

浏览量:9608次2021-01-20 09:27:42

-

浏览量:6086次2021-01-20 09:58:57

-

浏览量:2434次2019-11-21 08:51:37

-

浏览量:4490次2021-01-18 17:57:51

-

浏览量:2199次2019-09-18 16:32:09

-

浏览量:3127次2020-06-16 09:36:17

-

浏览量:1227次2023-03-21 10:37:02

-

浏览量:2298次2019-11-27 16:00:08

-

浏览量:4708次2021-01-07 15:03:29

-

浏览量:5793次2019-11-09 09:37:38

-

浏览量:2470次2019-03-09 13:18:53

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

技术凯

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友