技术专栏

Cortex M3 SoC芯片-AHB总线

本文结构层次:(一)首先,AHB总线的接口信号列表;(二)其次,AHB的传输类型时序图;

(三)最后,AHB的实例波形图;

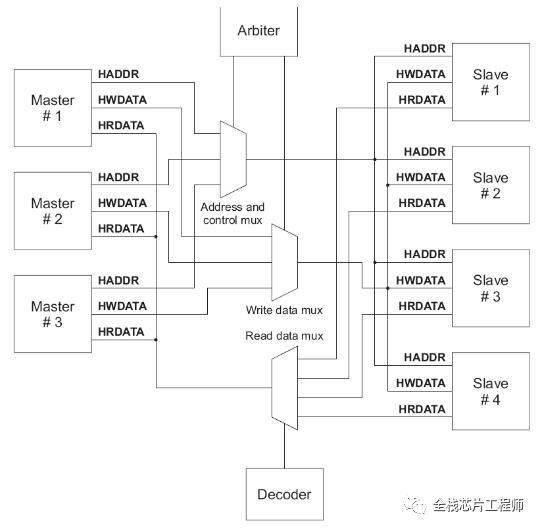

Cortex M3 SoC芯片-AHB总线的简要架构图如下:

H:以H为开头代表AHB总线信号,以区别其他总线信号;

n:低电平有效,如HRESETn,低电平有效,也是AHB协议里唯一的低电平有效信号。

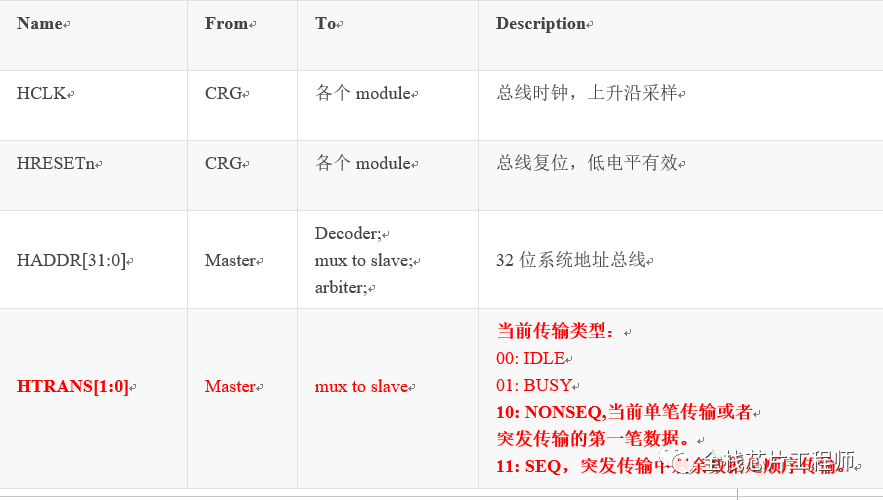

x:针对某一Master或Slave的信号,如HBUSREQx1为Master1的bus request信号。(一)首先,AHB总线的接口信号列表;

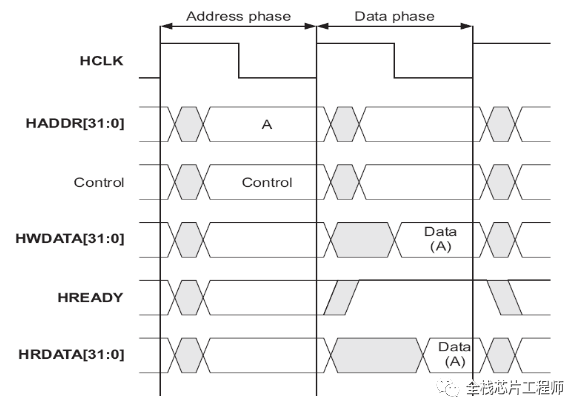

(二)其次,AHB的传输类型时序图;- 简单传输

一笔transfer由地址段、数据段组成。

-

HCLK第一个上升沿Master驱动地址、控制信号;

-

HCLK第二个上升沿Slave采集地址、控制信号;

此时,读操作的话,Slave准备好读数据;写操作的话,Master准备好写数据;

-

HCLK第三个上升沿,完成读写数据的锁存。流水线:

当前transfer的地址段传输的同时,上一笔transfer的数据段也在传输,满足高速传输需求。

-

等待状态

有等待状态的传输上,写数据操作Master必须保持总线上的写数据稳定,而读取数据操作只需要Slave在传输完成前的一个周期提供有效的数据。

-

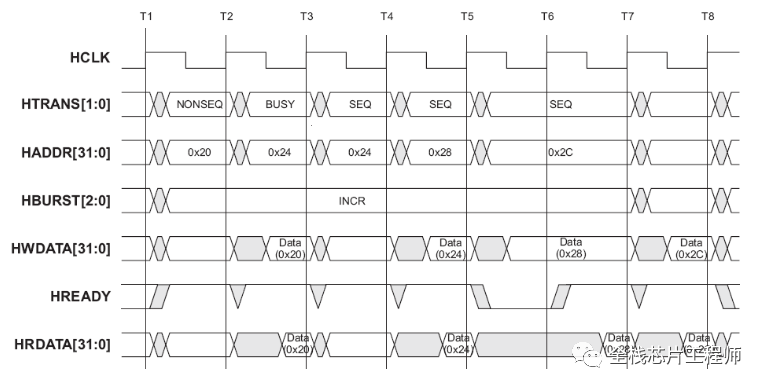

多笔传输

-

HTRANS(带BUSY)、且有等待状态的时序图

Burst的第一笔传输为NONSEQ;下一周期Master无法及时提供输出数据,因此BUSY延迟下一笔传输;第三笔传输Master立即发出但Slave没准备好,HREADY加入一拍等待;第四笔传输不用等待直接完成。

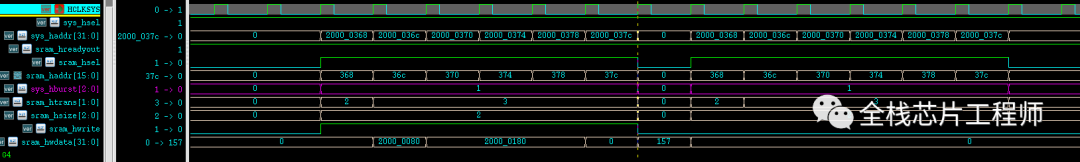

(三)最后,AHB的实例波形图;

感谢阅读文章,如果文章有用,麻烦点个“在看”或转发分享。

转载:全栈芯片工程师

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

点赞

收藏

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:2325次2022-01-24 09:00:14

-

浏览量:2679次2022-02-28 09:00:12

-

浏览量:7427次2022-05-10 12:41:18

-

浏览量:1142次2023-03-06 15:11:21

-

浏览量:7052次2022-05-09 11:00:58

-

浏览量:3796次2020-08-13 11:43:30

-

浏览量:5022次2020-11-14 09:41:56

-

浏览量:4974次2020-08-13 11:41:54

-

浏览量:3266次2022-01-21 09:00:16

-

浏览量:5065次2023-04-14 17:15:24

-

浏览量:3199次2019-11-27 17:25:21

-

浏览量:4128次2019-03-07 20:33:59

-

浏览量:2578次2020-08-03 11:18:53

-

浏览量:3725次2020-08-10 09:24:28

-

浏览量:4955次2018-05-25 21:45:17

-

浏览量:2903次2022-01-11 09:00:14

-

浏览量:2695次2022-02-04 09:00:28

-

浏览量:3028次2022-11-16 18:17:20

-

浏览量:3325次2020-12-31 09:42:35

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

david

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友