技术专栏

UVM Sequence基础及仲裁机制

sequence机制

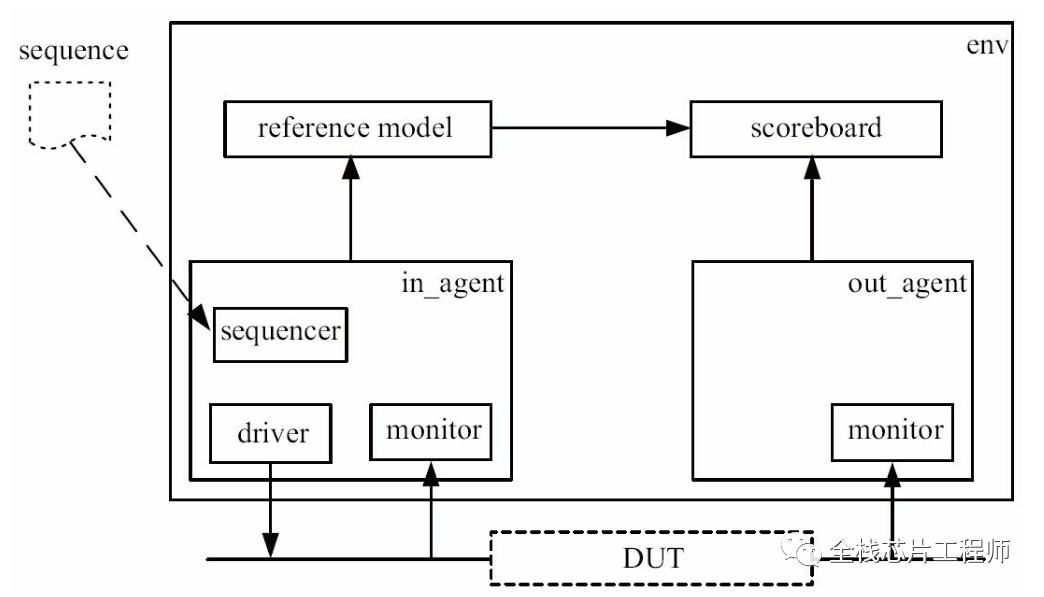

sequence机制用于产生激励,它是UVM中最重要的机制之一。

在一个规范化的UVM验证平台中,driver只负责驱动transaction,而不负责产生transaction。虽然将激励放在driver的main_phase中也是可行的,但是如果要对激励作修改,则扩展性较差,所以规范化的UVM验证平台中,我们将激励改为放在sequence中去写。

sequence机制有两大组成部分,一是sequence,二是sequencer。driver就负责驱动激励,激励内容由sequence完成。只有在sequencer的帮助下,sequence产生出的transaction才能最终送给driver。

sequence就像是一个弹夹,里面的子弹是transaction,而sequencer是一把

枪。

在不同的测试用例中,将不同的sequence设置成sequencer的main_phase的default_sequence。当sequencer执行到main_phase时,发现有default_sequence,那么它就启动sequence。

Sequence启动

当定义完一个sequence后,可以使用start任务将其启动。

<pre class="code-snippet__js" data-lang="makefile">```

<span class="code-snippet_outer">my_sequence my_seq;</span>my_seq = my_sequence::type_id::create("my_seq");

<span class="code-snippet_outer">my_seq.start(sequencer);</span>

除了上述直接启动之外,还可以使用default\_sequence启动。

-

-

-

-

``` uvm_config_db#(uvm_object_wrapper)::set(this, `````` "env.i_agt.sqr.main_phase", `````` "default_sequence", `````` case0_sequence::type_id::get()); ``` ``` 还可以先实例化要启动的sequence,之后再通过default\_sequence启动: - - - - - - - - - `````` function void my_case0::build_phase(uvm_phase phase); `````` case0_sequence cseq; `````` super.build_phase(phase); `````` cseq = new("cseq"); `````` uvm_config_db#(uvm_sequence_base)::set(this, `````` "env.i_agt.sqr.main_phase", `````` "default_sequence", `````` cseq); `````` endfunction ``` ``` 当一个sequence启动后会自动执行sequence的body任务。其实,除了body外,还会自动调用sequence的pre\_body与post\_body: - - - - - - - - - - - - - `````` class case0_sequence extends uvm_sequence #(my_transaction); `````` virtual task pre_body(); `````` `uvm_info("sequence0", "pre_body is called!!!", UVM_LOW) `````` endtask `````` virtual task post_body(); `````` `uvm_info("sequence0", "post_body is called!!!", UVM_LOW) `````` endtask `````` virtual task body(); `````` #100; `````` `uvm_info("sequence0", "body is called!!!", UVM_LOW) `````` endtask `````` `uvm_object_utils(case0_sequence) `````` endclass ``` ``` **sequence的仲裁机制** UVM支持在同一个sequencer上可以启动多个sequence。 在my\_sequencer上同时启动了两个sequence:sequence1和sequence2,代码如下所示: - - - - - - - - - - - - `````` task my_case0::main_phase(uvm_phase phase); `````` sequence0 seq0; `````` sequence1 seq1; `````` seq0 = new("seq0"); `````` seq0.starting_phase = phase; `````` seq1 = new("seq1"); `````` seq1.starting_phase = phase; `````` fork `````` seq0.start(env.i_agt.sqr); `````` seq1.start(env.i_agt.sqr); `````` join `````` endtask ``` ``` 其中sequence0的定义为: - - - - - - - - - - - - `````` class sequence0 extends uvm_sequence #(my_transaction); `````` virtual task body(); ``````

`````` repeat (5) begin `````` `uvm_do(m_trans) `````` `uvm_info("sequence0", "send one transaction", UVM_MEDIUM) `````` end `````` #100; ``````

`````` endtask `````` `uvm_object_utils(sequence0) `````` endclass ``` ``` sequence1的定义为: - - - - - - - - - - - - `````` class sequence1 extends uvm_sequence #(my_transaction); `````` virtual task body(); ``````

`````` repeat (5) begin `````` `uvm_do_with(m_trans, {m_trans.pload.size `````` `uvm_info("sequence1", "send one transaction", UVM_MEDIUM) `````` end `````` #100; ``````

`````` endtask `````` `uvm_object_utils(sequence1) `````` endclass ``` ``` 当使用uvm\_do或者uvm\_do\_with宏时,产生的transaction的优先级是默认的优先级,即-1,这个数值必须是一个大于等于-1的整数。数字越大,优先级越高。 运行如上代码后,会显示两个sequence交替产生transaction: - - - - - - `````` # UVM_INFO my_case0.sv(15) @ 85900: uvm_test_top.env.i_agt.sqr@@seq0 [sequence0] send one transaction `````` # UVM_INFO my_case0.sv(37) @ 112500: uvm_test_top.env.i_agt.sqr@@seq1 [sequence1] send one transaction `````` # UVM_INFO my_case0.sv(15) @ 149300: uvm_test_top.env.i_agt.sqr@@seq0 [sequence0] send one transaction `````` # UVM_INFO my_case0.sv(37) @ 200500: uvm_test_top.env.i_agt.sqr@@seq1 [sequence1] send one transaction `````` # UVM_INFO my_case0.sv(15) @ 380700: uvm_test_top.env.i_agt.sqr@@seq0 [sequence0] send one transaction `````` # UVM_INFO my_case0.sv(37) @ 436500: uvm_test_top.env.i_agt.sqr@@seq1 [sequence1] send one transaction ``` ``` **Sequence仲裁机制** **1、transaction的优先级** 可以通过uvm\_do\_pri及uvm\_do\_pri\_with改变所产生的transaction的优先级: - - - - - - - - - - - - - - - - - - - - - - - - - - `````` class sequence0 extends uvm_sequence #(my_transaction); `````` … `````` 10 virtual task body(); `````` … `````` 13 repeat (5) begin `````` 14 `uvm_do_pri(m_trans, 100) `````` 15 `uvm_info("sequence0", "send one transaction", UVM_MEDIUM) `````` 16 end `````` 17 #100; `````` … `````` 20 endtask `````` … `````` 23 endclass `````` 24 `````` 25 class sequence1 extends uvm_sequence #(my_transaction); `````` … `````` 32 virtual task body(); `````` … `````` 35 repeat (5) begin `````` 36 `uvm_do_pri_with(m_trans, 200, {m_trans.pload.size `````` 37 `uvm_info("sequence1", "send one transaction", UVM_MEDIUM) `````` 38 end `````` … `````` 42 endtask `````` … `````` 45 endclass ``` ``` uvm\_do\_pri与uvm\_do\_pri\_with的第二个参数是优先级,这个数值必须是一个大于等于-1的整数。数字越大,优先级越高。 但是运行上述代码,发现并没有如预期的那样,而是sequence0与sequence1交替产生transaction。这是因为,在默认情况下sequencer的仲裁算法是SEQ\_ARB\_FIFO。它会严格遵循先入先出的顺序,而不会考虑优先级。 但这里存在sequencer的仲裁算法: - - - - - - `````` SEQ_ARB_FIFO, `````` SEQ_ARB_WEIGHTED, `````` SEQ_ARB_RANDOM, `````` SEQ_ARB_STRICT_FIFO, `````` SEQ_ARB_STRICT_RANDOM, `````` SEQ_ARB_USER ``` ``` 在默认情况下sequencer的仲裁算法是SEQ\_ARB\_FIFO。它会严格遵循先入先出的顺序,而不会考虑优先级。 SEQ\_ARB\_WEIGHTED是加权的仲裁; SEQ\_ARB\_RANDOM是完全随机选择; SEQ\_ARB\_STRICT\_FIFO是严格按照优先级的,当有多个同一优先级的sequence时,按照先入先出的顺序选择; SEQ\_ARB\_STRICT\_RANDOM是严格按照优先级的,当有多个同一优先级的sequence时,随机从最高优先级中选择; SEQ\_ARB\_USER则是用户可以自定义一种新的仲裁算法。 因此,若想使优先级起作用,应该设置仲裁算法为SEQ\_ARB\_STRICT\_FIFO或者SEQ\_ARB\_STRICT\_RANDOM: 因此,my\_case0代码改为如下: - - - - - - - - `````` task my_case0::main_phase(uvm_phase phase); `````` … `````` env.i_agt.sqr.set_arbitration(SEQ_ARB_STRICT_FIFO); `````` fork `````` seq0.start(env.i_agt.sqr); `````` seq1.start(env.i_agt.sqr); `````` join `````` endtask ``` ``` 经过如上的设置后,会发现直到sequence1发送完transaction后,sequence0才开始发送。 **Sequence仲裁机制** **2、sequence的优先级** 除transaction有优先级外,sequence也有优先级的概念。可以在sequence启动时指定其优先级。 start任务的第一个参数是sequencer,第二个参数是parent sequence,可以设置为null,第三个参数是优先级,如果不指定则此值为-1,它同样不能设置为一个小于-1的数字。这个数值必须是一个大于等于-1的整数。数字越大,优先级越高。 - - - - - - - `````` task my_case0::main_phase(uvm_phase phase); `````` env.i_agt.sqr.set_arbitration(SEQ_ARB_STRICT_FIFO); `````` fork `````` seq0.start(env.i_agt.sqr, null, 100); `````` seq1.start(env.i_agt.sqr, null, 200); `````` join `````` endtask ``` ``` 运行上述代码,会发现sequence1中的transaction完全发送完后才发送sequence0中的transaction。 即不在uvm\_do系列宏中指定优先级。运行上述代码,会发现 sequence1中的transaction完全发送完后才发送sequence0中的transaction。所以,对sequence设置优先级的本质即设置其内产生的 transaction的优先级。 **Sequencer lock操作** lock操作,就是sequence向sequencer发送一个请求,这个请求与其他sequence发送transaction的请求一同被放入sequencer的仲裁队列中。当其前面的所有请求被处理完毕后,sequencer就开始响应这个lock请求,此后sequencer会一直连续发送此sequence的transaction,直到unlock操作被调用。从效果上看,此sequencer的所有权并没有被所有的sequence共享,而是被申请lock操作的sequence独占了。一个使用lock操作的sequence为: - - - - - - - - - - - - - - - - - - - - `````` class sequence1 extends uvm_sequence #(my_transaction); `````` virtual task body(); `````` repeat (3) begin `````` `uvm_do_with(m_trans, {m_trans.pload.size `````` `uvm_info("sequence1", "send one transaction", UVM_MEDIUM) `````` end `````` lock(); `````` `uvm_info("sequence1", "locked the sequencer ", UVM_MEDIUM) `````` repeat (4) begin `````` `uvm_do_with(m_trans, {m_trans.pload.size 500;}) `````` `uvm_info("sequence1", "send one transaction", UVM_MEDIUM) `````` end `````` `uvm_info("sequence1", "unlocked the sequencer ", UVM_MEDIUM) `````` unlock(); `````` repeat (3) begin `````` `uvm_do_with(m_trans, {m_trans.pload.size `````` `uvm_info("sequence1", "send one transaction", UVM_MEDIUM) `````` end `````` endtask `````` endclass ``` ``` 将此sequence1与下面的sequence0在env.i\_agt.sqr上启动, - - - - - - - - - - - - - - `````` 3 class sequence0 extends uvm_sequence #(my_transaction); `````` … `````` 10 virtual task body(); `````` … `````` 13 repeat (5) begin `````` 14 `uvm_do(m_trans) `````` 15 `uvm_info("sequence0", "send one transaction", UVM_MEDIUM) `````` 16 end `````` 17 #100; `````` … `````` 20 endtask `````` 21 `````` 22 `uvm_object_utils(sequence0) `````` 23 endclass ``` ``` 在env.i\_agt.sqr上启动, - - - - - - - - - - - - - `````` task my_case0::main_phase(uvm_phase phase); `````` 58 sequence0 seq0; `````` 59 sequence1 seq1; `````` 60 `````` 61 seq0 = new("seq0"); `````` 62 seq0.starting_phase = phase; `````` 63 seq1 = new("seq1"); `````` 64 seq1.starting_phase = phase; `````` 65 fork `````` 66 seq0.start(env.i_agt.sqr); `````` 67 seq1.start(env.i_agt.sqr); `````` 68 join `````` 69 endtask ``` ``` 会发现在lock语句前,sequence0和seuquence1交替产生transaction;在lock语句后,一直发送sequence1的transaction,直到unlock语句被调用后,sequence0和seuquence1又开始交替产生transaction。 如果两个sequence都试图使用lock任务来获取sequencer的所有权则会如何呢?答案是先获得所有权的sequence在执行完毕后才 会将所有权交还给另外一个sequence。 **Sequence grab操作** 与lock操作一样,grab操作也用于暂时拥有sequencer的所有权,只是grab操作比lock操作优先级更高。lock请求是被插入sequencer仲裁队列的最后面,等到它时,它前面的仲裁请求都已经结束了。grab请求则被放入sequencer仲裁队列的最前面,它几乎是一发出就拥有了sequencer的所有权。 - - - - - - - - - - - - - - - - - - - - - `````` class sequence1 extends uvm_sequence #(my_transaction); `````` virtual task body(); `````` repeat (3) begin `````` `uvm_do_with(m_trans, {m_trans.pload.size `````` `uvm_info("sequence1", "send one transaction", UVM_MEDIUM) `````` end `````` grab(); `````` `uvm_info("sequence1", "grab the sequencer ", UVM_MEDIUM) `````` repeat (4) begin `````` `uvm_do_with(m_trans, {m_trans.pload.size 500;}) `````` `uvm_info("sequence1", "send one transaction", UVM_MEDIUM) `````` end `````` `uvm_info("sequence1", "ungrab the sequencer ", UVM_MEDIUM) `````` ungrab(); `````` repeat (3) begin `````` `uvm_do_with(m_trans, {m_trans.pload.size `````` `uvm_info("sequence1", "send one transaction", UVM_MEDIUM) `````` end `````` endtask `````` `uvm_object_utils(sequence1) `````` endclass ``` ``` 如果两个sequence同时试图使用grab任务获取sequencer的所有权将会如何呢?这种情况与两个sequence同时试图调用lock函数一样,在先获得所有权的sequence执行完毕后才会将所有权交还给另外一个试图所有权的sequence。 如果一个sequence在使用grab任务获取sequencer的所有权前,另外一个sequence已经使用lock任务获得了sequencer的所有权则会如何呢?答案是grab任务会一直等待lock的释放。grab任务还是比较讲文明的,虽然它会插队,但是绝不会打断别人正在进行的事情。 **Sequence的有效性** 当有多个sequence同时在一个sequencer上启动时,所有的sequence都参与仲裁,根据算法决定哪个sequence发送transaction。仲裁算法是由sequencer决定的,sequence除了可以在优先级上进行设置外,对仲裁的结果无能为力。 通过lock任务和grab任务,sequence可以独占sequencer,强行使sequencer发送自己产生的transaction。同样的,UVM也提供措施使sequence可以在一定时间内不参与仲裁,即令此sequence失效。 sequencer在仲裁时,会查看sequence的is\_relevant函数的返回结果。如果为1,说明此sequence有效,否则无效。因此可以通过重载is\_relevant函数来使sequence失效: 文章内容参考自:张强《UVM实战》 感谢阅读,别走!点赞、关注、转发后再走吧  转载:全栈芯片工程师

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

点赞

收藏

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:14006次2022-02-10 09:00:10

-

浏览量:1473次2023-12-11 15:57:50

-

浏览量:2447次2018-12-02 13:00:27

-

浏览量:4213次2024-02-22 15:52:02

-

浏览量:1046次2023-09-28 11:44:09

-

浏览量:10426次2021-04-20 15:42:26

-

浏览量:5109次2019-09-01 11:15:39

-

浏览量:9422次2020-12-09 10:16:29

-

浏览量:1179次2023-08-18 17:31:53

-

浏览量:1997次2023-04-17 15:56:29

-

浏览量:3334次2023-12-13 17:20:20

-

浏览量:9994次2020-12-18 22:21:10

-

浏览量:1881次2019-11-01 17:34:24

-

浏览量:3495次2019-11-19 14:40:18

-

浏览量:15177次2021-06-15 10:27:34

-

浏览量:3622次2024-01-12 17:23:50

-

浏览量:1713次2023-03-01 11:22:14

-

浏览量:2344次2021-01-27 16:48:37

-

浏览量:1783次2024-01-25 14:14:02

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

david

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友