技术专栏

解析AXI4.0 Slave接口设计

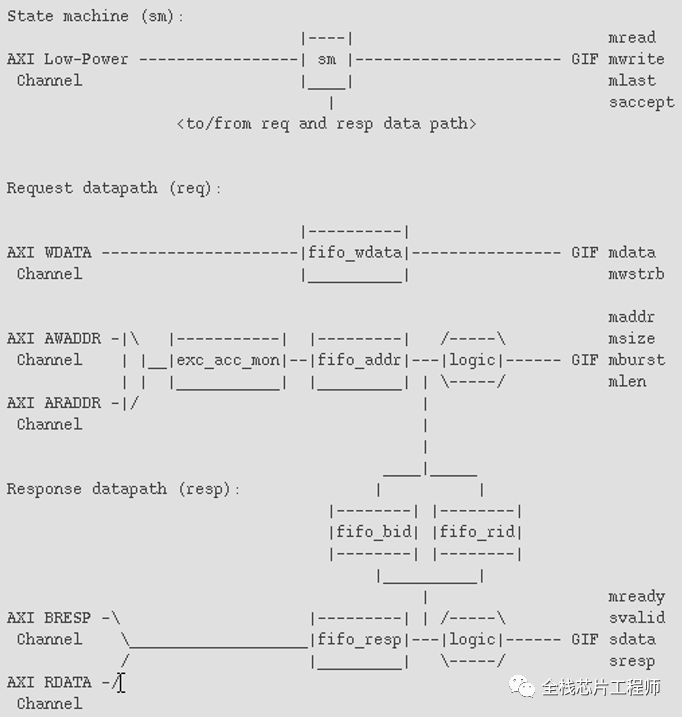

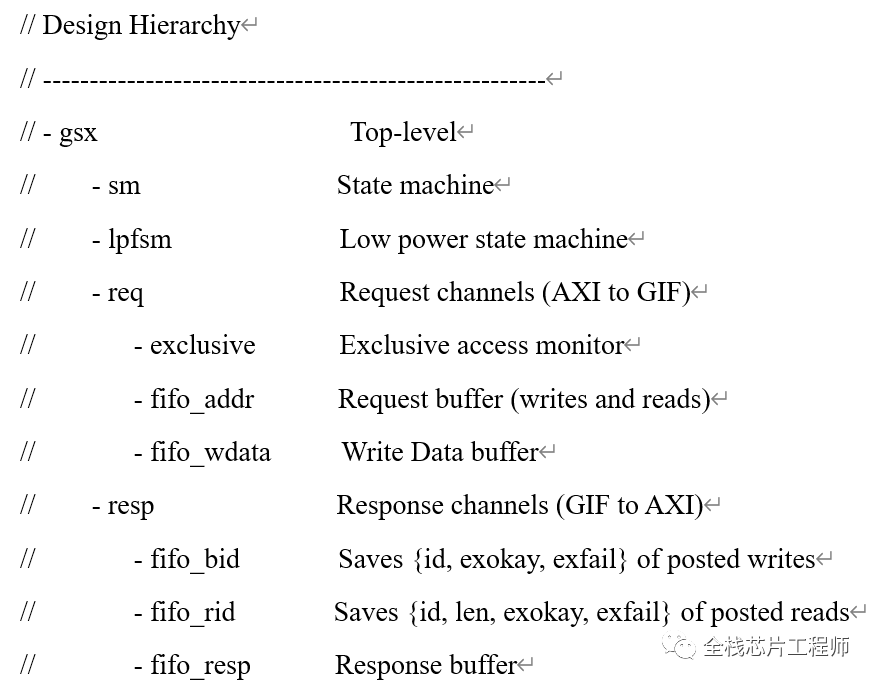

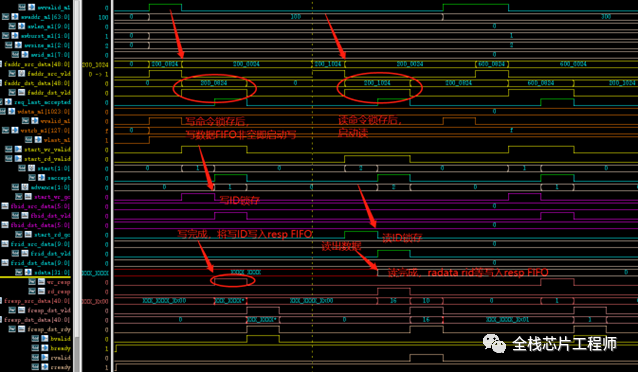

本文节选自【全栈芯片工程师】知识星球。解析AXI4.0 Slave接口设计,代码结构非常精简,如下图:

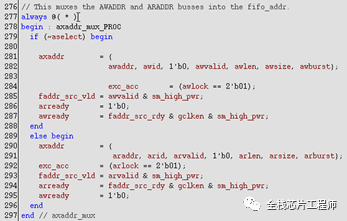

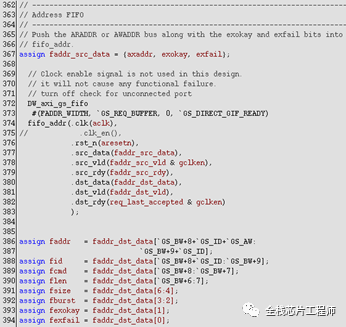

首先,读写地址通道共用一个FIFO且采用读写交错方式存储。

将awaddr、awid、awvalid、awlen、awsize、awburst等信息寄存到FIFO_ADDR,在FIFO_ADDR非空、状态机允许情况下,回一个awready给master完成握手。gclken目前接的常1。

将wdata、wstrb等信息寄存到FIFO_WDATA,在FIFO非空、状态机允许情况下,回一个wready给master完成握手。gclken目前接的常1。

原文内容参见知识星球。

欢迎加入【全栈芯片工程师】知识星球,手把手教你设计MCU、ISP图像处理,从算法、前端、DFT到后端全流程设计。

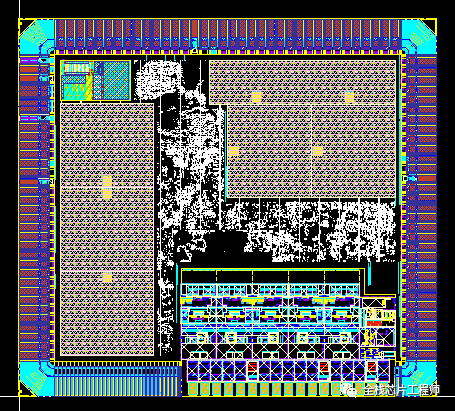

实战MCU+ISP图像处理芯片版图

实战ISP图像算法效果

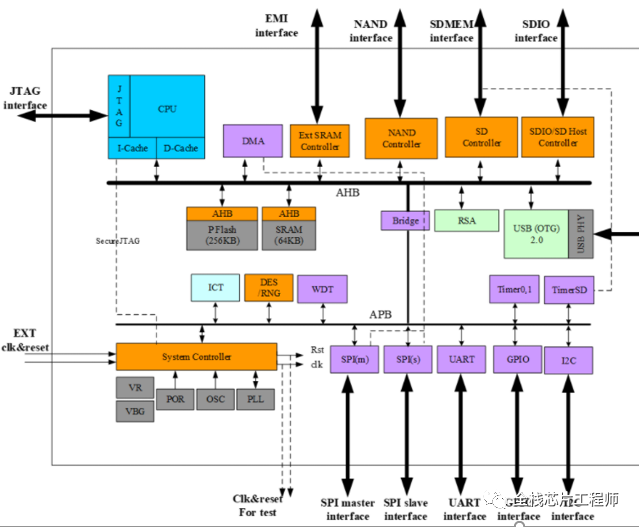

知识星球发起MCU项目启动,大家一起参与MCU项目规格启动讨论,我把设计、验证、DFT、后端的知识点全部罗列出来,大家一起来完善。

以项目驱动的方式介绍MCU芯片全流程设计的方法;提炼相关的检查列表、signoff checklist的样本;让星球成员熟悉SoC架构、设计流程、开发进度、项目管理;

AXI的非突发写、读仿真波形如下:

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

点赞

收藏

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:8647次2022-05-11 08:10:28

-

浏览量:16914次2021-07-12 23:53:03

-

浏览量:3604次2020-11-27 10:06:38

-

浏览量:13503次2022-06-10 21:31:53

-

浏览量:13258次2020-08-23 21:54:03

-

浏览量:2373次2020-07-07 09:07:51

-

浏览量:17422次2018-09-27 20:15:39

-

浏览量:12986次2022-06-10 21:26:04

-

浏览量:1875次2024-05-27 19:35:18

-

浏览量:6029次2021-04-10 14:21:38

-

浏览量:5677次2021-04-10 14:11:46

-

浏览量:3014次2020-08-21 14:05:19

-

浏览量:18223次2020-12-03 00:29:52

-

浏览量:3676次2020-11-21 16:48:04

-

浏览量:4030次2020-08-05 20:46:02

-

浏览量:1985次2023-04-19 09:13:30

-

浏览量:2457次2020-08-05 20:47:40

-

浏览量:4938次2021-04-16 10:56:40

-

浏览量:1503次2023-05-06 13:40:15

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

南宫醉

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友