技术专栏

IIR数字滤波器的设计

基于FPGA IIR数字滤波器的设计

IIR(Infinite Impulse Response)无线脉冲响应滤波器。

系统传递函数为:

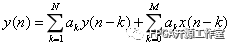

系统的差分方程可写为:

IIR优缺点:

1)在相同的幅频条件下,滤波器阶数比FIR滤波器低。

2)IIR滤波器占用的硬件资源比较少(相比FIR滤波器)。

3)不具备严格的线性相位特性。

1 IIR数字滤波器的基本结构及类型

图1 直接I型

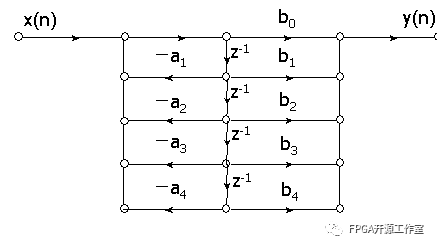

图2 直接II型

图3 级联型

图4 并联型

2 设计目标

采用matlab buffer函数设计一个IIR滤波器低通滤波器,通带截止频率为1khz,输入信号为1khz+3khz sin波形,经过IIR滤波器后输出为1KHZ sin波,其他不做要求。(本文只对IIR设计思想进行验证不做性能要求)。

3 matlab的设计验证

Matlab源码:

%参数定义

<pre code="" consolas="" courier="" inconsolata="" menlo="" monaco="" mono="" monospace="" pro="" rgb="" sans="" sans-serif="" sc="" source="" style="box-sizing: border-box;font-family: " yahei="">```

FS <span style="box-sizing: border-box;color: rgb(166, 127, 89);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">=</span><span style="box-sizing: border-box;color: rgb(152, 104, 1);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">44100</span><span style="box-sizing: border-box;color: rgb(153, 153, 153);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">;</span> <span style="box-sizing: border-box;color: rgb(166, 127, 89);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">%</span>Sample rate Frequncy<br></br>fc <span style="box-sizing: border-box;color: rgb(166, 127, 89);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">=</span> <span style="box-sizing: border-box;color: rgb(152, 104, 1);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">1000</span><span style="box-sizing: border-box;color: rgb(153, 153, 153);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">;</span> <span style="box-sizing: border-box;color: rgb(166, 127, 89);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">%</span><span style="box-sizing: border-box;color: rgb(152, 104, 1);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">1</span>khz<br></br>fe <span style="box-sizing: border-box;color: rgb(166, 127, 89);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">=</span> <span style="box-sizing: border-box;color: rgb(152, 104, 1);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">3000</span><span style="box-sizing: border-box;color: rgb(153, 153, 153);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">;</span> <span style="box-sizing: border-box;color: rgb(166, 127, 89);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">%</span>外部输入信号 <span style="box-sizing: border-box;color: rgb(152, 104, 1);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">3</span>khz<br></br>N <span style="box-sizing: border-box;color: rgb(166, 127, 89);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">=</span> <span style="box-sizing: border-box;color: rgb(152, 104, 1);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">1024</span><span style="box-sizing: border-box;color: rgb(153, 153, 153);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">;</span><br></br>Q <span style="box-sizing: border-box;color: rgb(166, 127, 89);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">=</span><span style="box-sizing: border-box;color: rgb(152, 104, 1);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">16</span><span style="box-sizing: border-box;color: rgb(153, 153, 153);font-variant-ligatures: normal !important;font-variant-numeric: normal !important;font-variant-east-asian: normal !important;font-stretch: normal !important;line-height: normal !important;">;</span><br></br>

%波形产生

``` sin_osc =sin(t*fc);

sin_e =sin(t*fe);

sin_add = sin_osc+sin_e;

``` ``` %IIR 滤波器系数(低通滤波器) `````` [b a] = butter(3,fc/(FS/2),'low');

%滤波(混频后)

y = filter(b,a,sin_add);

f_osc =fft(sin_osc,N);

f_osc=20*log(abs(f_osc))/log(10); %换算成dBW单位

ft=[0:(FS/N):FS/2]; %转换横坐标以Hz为单位

f_osc=f_osc(1:length(ft));

``` ``` %滤波器系数量化 `````` Mab =max(max(abs(a),abs(b)));

%16bit 量化

Qb = round((b/Mab)*(2^(Q-1)-1));

Qa = round((a/Mab)*(2^(Q-1)-1));

%%%%

Qm =floor(log2(Mab/a(1)));

if Qmlog2(Mab/a(1))

Qm = Qm +1;

end

Qm = 2^Qm;

Qb1=round(b/Qm*(2^(Q-1)-1));

Qa1=round(a/Qm*(2^(Q-1)-1));

``` ``` %绘图 %时域波形图 `````` figure(1),

hold on

subplot(221),plot(t(1:128),sin_osc(1:128),'-');

legend('sin 1khz');title('sin 1khz');

subplot(222),plot(t(1:128),sin_e(1:128),'-');

legend('sin 3khz');title('sin 3khz');

subplot(223),plot(t(1:128),sin_add(1:128),'-');

legend('sin 1khz add 3khz');title('sin 1khz add 3khz');

subplot(224),plot(t(1:128),y(1:128),'-');

legend('LPF 结果');title('LPF 结果');

grid;

hold off

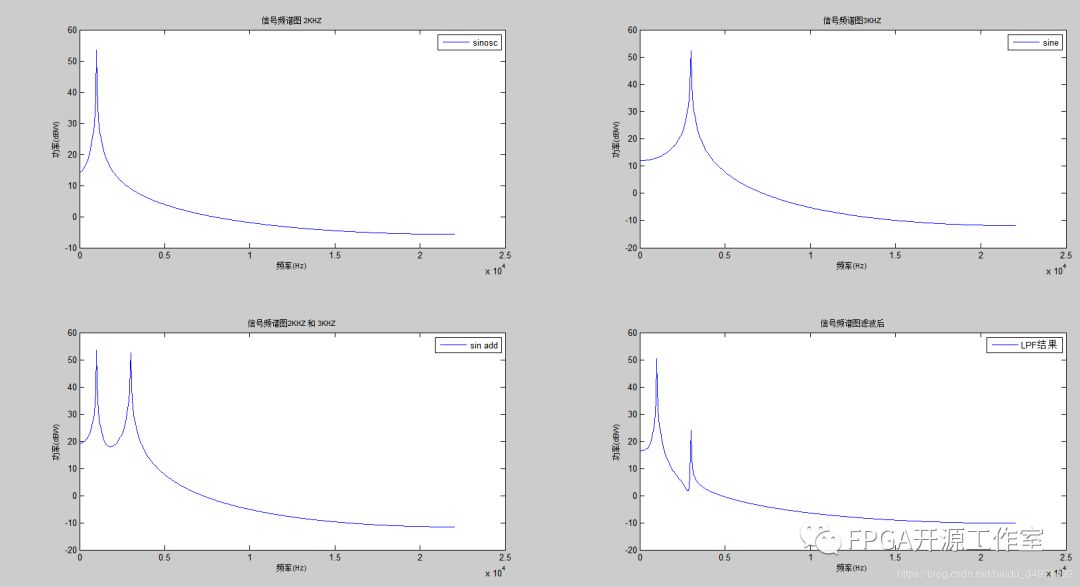

``` ``` %频域波形 `````` figure(2),

hold on

subplot(221);plot(ft,f_osc);

xlabel('频率(Hz)','fontsize',8); ylabel('功率(dBW)','fontsize',8);

title('信号频谱图 2KHZ','fontsize',8);legend('sinosc');

subplot(222);plot(ft,f_e);

xlabel('频率(Hz)','fontsize',8); ylabel('功率(dBW)','fontsize',8);

title('信号频谱图3KHZ','fontsize',8);legend('sine');

subplot(223);plot(ft,f_add);

xlabel('频率(Hz)','fontsize',8); ylabel('功率(dBW)','fontsize',8);

title('信号频谱图2KHZ 和 3KHZ','fontsize',8);legend('sin add');

subplot(224);plot(ft,y_f);

xlabel('频率(Hz)','fontsize',8); ylabel('功率(dBW)','fontsize',8);

title('信号频谱图滤波后','fontsize',8);legend('LPF结果');

hold off

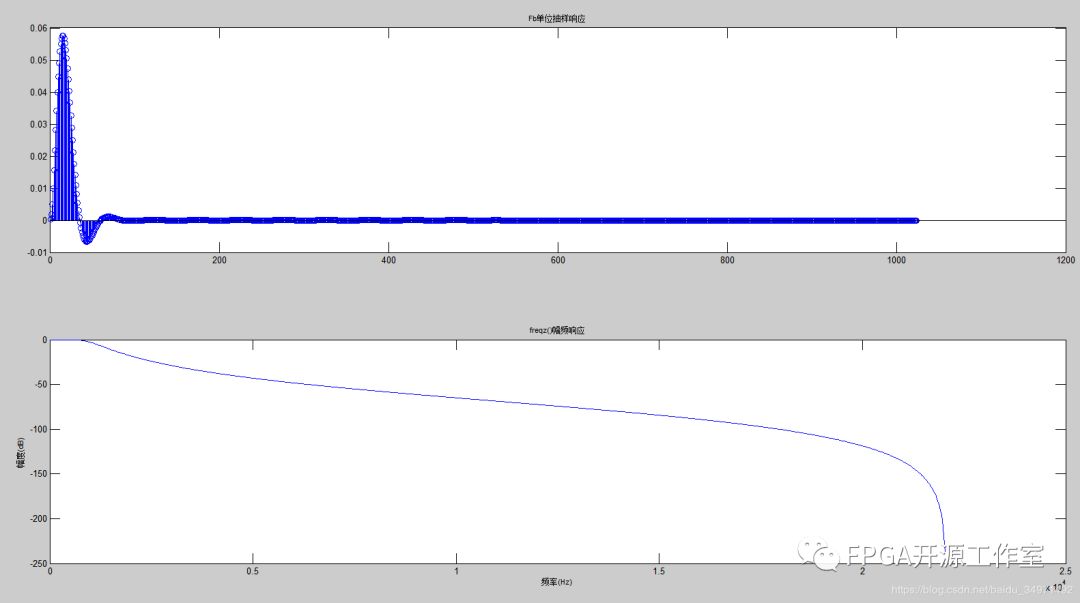

``` ``` %幅频响应 `````` figure(3);

subplot(211);stem(Fb);

title('Fb单位抽样响应','fontsize',8);

subplot(212);plot(f,mag);

xlabel('频率(Hz)','fontsize',8);

ylabel('幅度(dB)','fontsize',8);

title('freqz()幅频响应','fontsize',8);

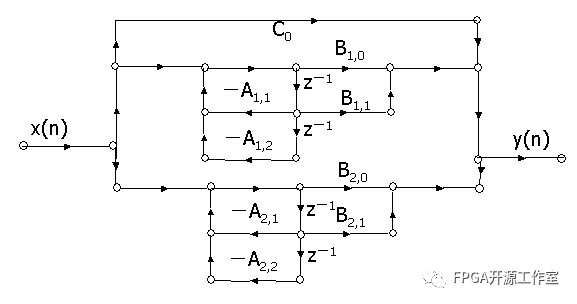

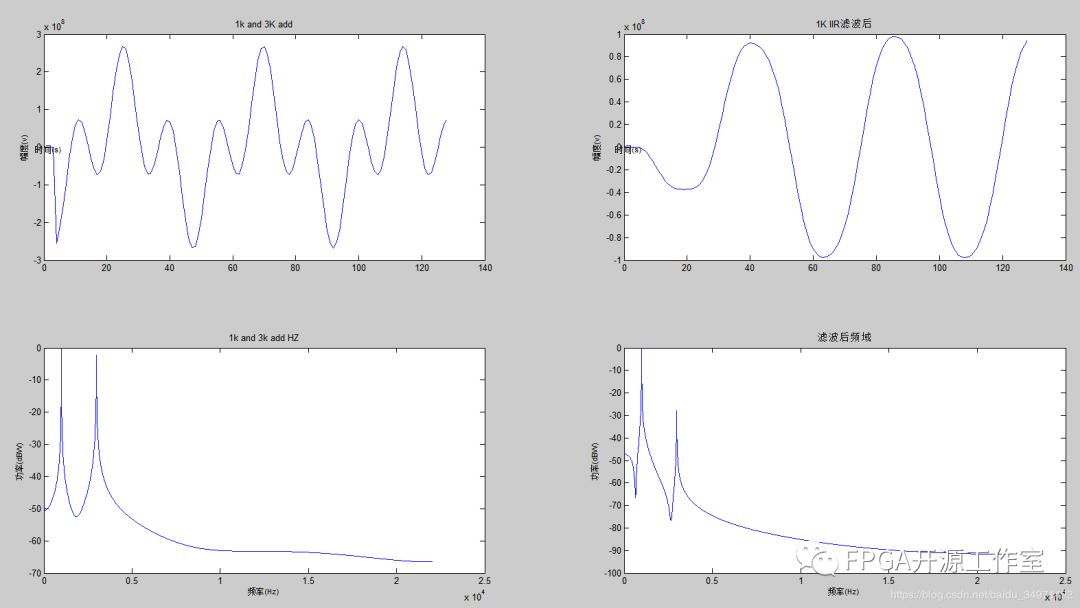

``` ```  图5 matlab时域波形如图5所示,(5,1)波形加(5,2)波形得到(5,3)波形,经过IIR滤波器后得到(5,4)时域波形。  图6 matlab频域分析如图6所示,(6,3)与(6,4)相比3khz大概被削弱25DB左右。  图7 IIR幅频响应分析 如图7所示,通过幅频响应(7,2)可知3khz所在位置大概被削弱25DB。 4 FPGA设计验证 ---------- FPGA IIR.v设计源码: `````` `timescale 1ps/1ps

module iir(

input mclk,//45.1584MHZ

input reset_n,

input signed[31:0] pcm_in,

output signed[31:0] pcm_out

);

localparam LAST_CYCLE = 1023;

reg [9:0] i;

wire signed [15:0] b1,b2,b3,b4;

wire signed [15:0] a2,a3,a4;

wire signed [31:0] xn;

reg signed [31:0] xn1,xn2,xn3;

reg signed [31:0] yn,yn1,yn2,yn3;

reg signed [47:0] r_x1;

reg signed [47:0] r_x2;

reg signed [47:0] r_y;

reg signed [47:0] r_s;

reg signed [47:0] r_s1;

//coffe b

assign b1 = 3;

assign b2 = 8;

assign b3 = 8;

assign b4 = 3;

//coffe a

assign a2 = -22243;

assign a3 = 20231;

assign a4 = -6159;

assign xn = pcm_in;

assign pcm_out = yn;

always @(posedge mclk or negedge reset_n) begin

if(reset_n == 1'b0) begin

i 0;

xn1 0;

xn2 0;

xn3 0;

yn 0;

yn1 0;

yn2 0;

yn3 0;

r_x1 0;

r_x2 0;

r_y 0;

r_s 0;

r_s1 0;

end

else begin

i i+1;

if(i==1) begin

r_x1 b1*(xn + xn3);

r_x2 b2*(xn1 + xn2);//Zero(n)

r_y a2*yn1+a3*yn2+a4*yn3;//Pole(n)

$display("r_x1 = %d,r_x2 = %d,r_y = %d",r_x1,r_x2,r_y);

end

if(i==2) begin

r_s r_x1 +r_x2 - r_y;//8192y(n) = Zero(n)-Pole(n)

$display("%d",r_s);

end

if(i==3) r_s1 (r_s>>13);

if(i==4) yn r_s1[31:0];

if(i==5) begin //pipeline

xn1 xn;

xn2 xn1;

xn3 xn2;

yn1 yn;

yn2 yn1;

yn3 yn2;

end

end

end

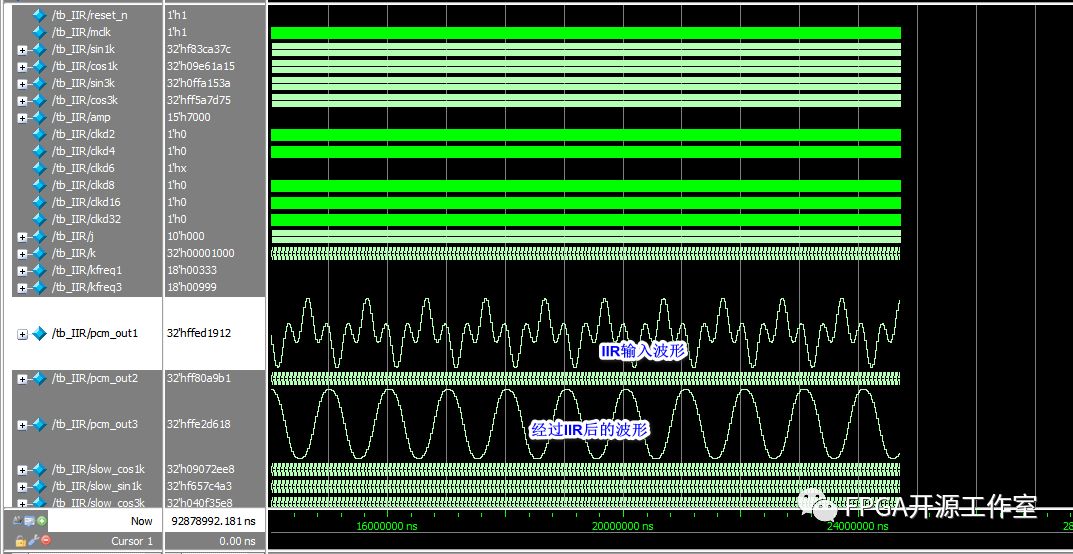

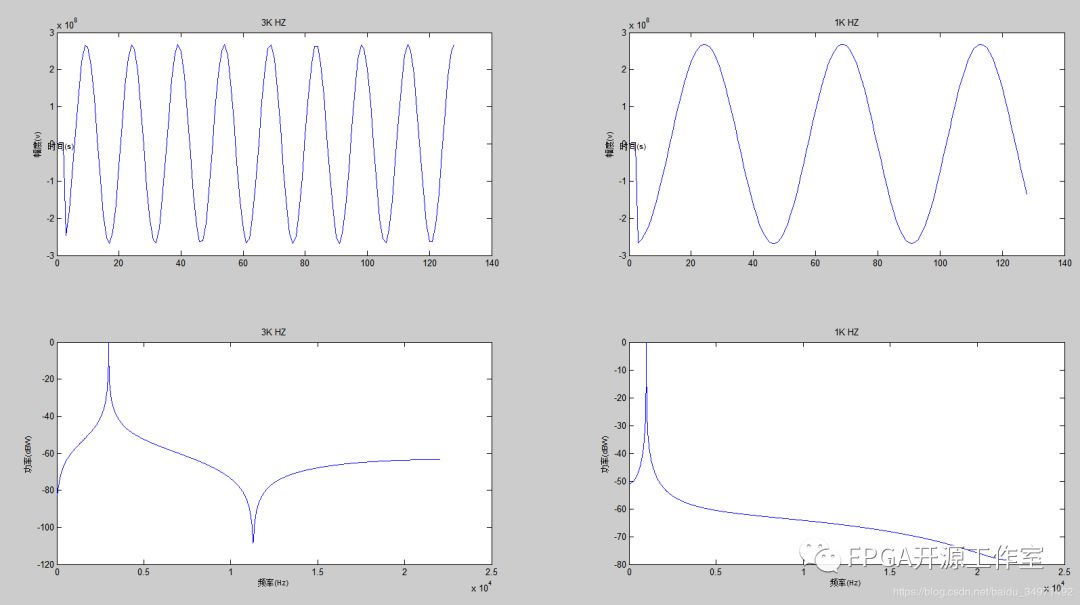

``` ``` Endmodule 实验结果: Modelsim波  图8 modelsim 时域波形由图8可知,pcm\_out1(1khz + 3khz)经过IIR滤波器后滤除了3khz,设计成功。 Matlab结果分析:  图9 FPGA输入波形matlab时域分析 图10 FPGA结果数据分析由图10的频域分析结果可知3khz大概被削弱25db左右,设计成功。 感谢阅读,别走!点赞、关注、转发后再走吧  转载:全栈芯片工程师

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

点赞

收藏

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:12938次2021-01-29 12:25:06

-

浏览量:19452次2021-01-21 11:45:55

-

浏览量:25050次2021-01-29 16:50:41

-

浏览量:5802次2022-02-13 09:00:13

-

浏览量:20652次2020-12-21 18:20:26

-

浏览量:18931次2021-01-18 13:46:39

-

浏览量:13944次2021-01-18 17:28:31

-

浏览量:7920次2021-01-20 08:36:19

-

浏览量:12967次2021-01-21 11:07:14

-

浏览量:6087次2021-01-20 09:58:57

-

浏览量:9612次2021-01-20 09:27:42

-

浏览量:2437次2019-11-21 08:51:37

-

浏览量:2459次2020-07-08 13:45:08

-

浏览量:2447次2020-07-28 17:27:40

-

浏览量:2200次2019-09-18 16:32:09

-

浏览量:1227次2023-03-21 10:37:02

-

浏览量:3130次2020-06-16 09:36:17

-

浏览量:4496次2021-01-18 17:57:51

-

浏览量:2301次2019-11-27 16:00:08

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

david

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友