技术专栏

虚拟时钟Virtual clock(一)

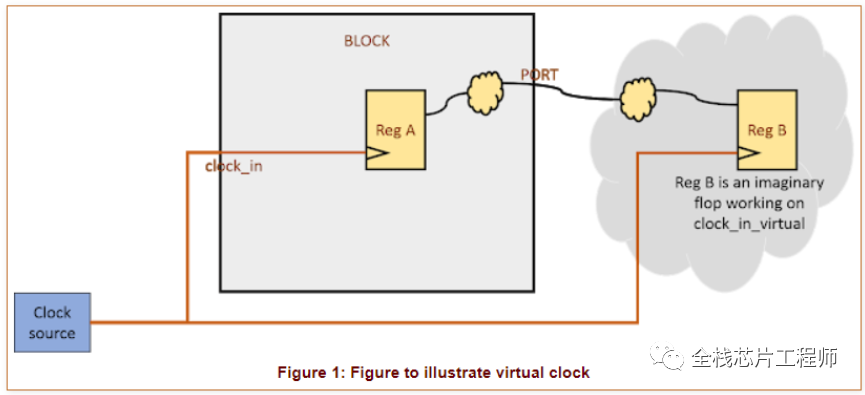

通常RTL设计要求对芯片/module的输入信号进行reg_in打拍处理,对芯片/module的输出也要求做reg_out打拍处理,这是良好的代码习惯,为时序收敛留下足够裕量,也避免顶层例化综合后的子模块时出现模块间IO时序不满足的情况。综合阶段可根据设计、工艺需求,设置IO的input/output为时钟周期的40%-60%。

但是,芯片timing sign off阶段会偶尔遇到IO时序少量违例,比如,输入reg的hold违例、输出reg的setup违例,本质原因是EDA时序分析工具会在输出输入外部假定一个理想化的不带clock propagation time的寄存器做时序分析。

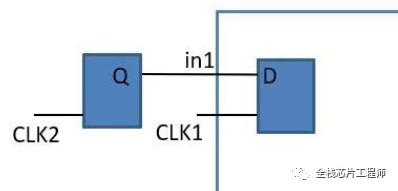

比如,在set_propagated_clock命令后,下图左边寄存器的CLK2端就不带clock propagation time,而CLK1(与CLK2同频同相)就带insertion delay, 拥有时钟latency,这样输入IO的hold违例就可能发生,setup反而更容易满足。

同理,在set_propagated_clock命令后,输出IO的setup违例就可能发生,hold反而更容易满足。

同理,在set_propagated_clock命令后,输出IO的setup违例就可能发生,hold反而更容易满足。

以输出IO的register的setup建立时间为例,launch clock的data path上由于存在1.5ns的propagation time/clock latency,发生了时序违例。这是因为外部假定的register是没有propagation time/clock latency。而保持时间则反而容易满足。

虚拟时钟应运而生,那么如何创建虚拟时钟?其有什么好处呢?

<pre class="code-snippet__js" data-lang="nginx">```

<span class="code-snippet_outer"><span class="code-snippet__attribute">create_clock</span> -name vclk -period <span class="code-snippet__number">10</span></span>

注意,创建虚拟时钟不用指定clk pin/port。

-

-

``` set_input_delay 8 -clock vclk [get_ports data_in ] `````` set_output_delay 8 -clock vclk [get_ports data_out] ``` ``` EDA工具会基于虚拟时钟,根据芯片/模块内部时钟的实际insertion delay评估IO外部假定寄存器的propagation time,这样时序分析就可以规避不必要的“假”违例,当然也可以不指定virtual clock,只是每次分析时序时都需要检查并排除这种“假”违例,影响了工作效率。 转载:全栈芯片工程师

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

点赞

收藏

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:4744次2021-12-26 09:00:15

-

浏览量:12263次2021-12-31 09:00:12

-

浏览量:7110次2022-06-08 21:18:55

-

浏览量:6943次2021-02-22 14:07:13

-

浏览量:10212次2020-11-14 15:42:52

-

浏览量:3375次2021-12-25 09:00:17

-

浏览量:10810次2021-12-11 15:15:27

-

浏览量:8367次2021-12-21 09:00:31

-

浏览量:2887次2021-10-14 17:11:05

-

浏览量:3468次2022-01-28 09:00:16

-

浏览量:7164次2020-03-18 10:41:44

-

浏览量:3914次2022-10-13 10:22:20

-

浏览量:1632次2023-03-13 11:04:56

-

浏览量:10267次2021-04-27 17:56:41

-

浏览量:3260次2022-05-30 11:53:09

-

浏览量:13480次2021-01-02 00:02:19

-

浏览量:7544次2023-12-25 14:11:19

-

浏览量:6794次2021-02-21 21:08:27

-

浏览量:2991次2020-08-20 18:03:14

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

david

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友