低功耗设计之Multi-Bit Cell

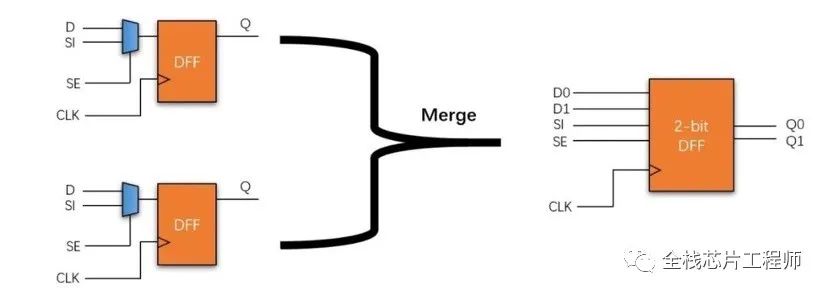

从Cadence user guide可以查阅到如下描述:Multi-bit flip-flop (MBFF) flow provides power optimization benefits with a minimum impact on timing. This flow is called as a part of the preCTS optimization stage.所谓multi-bit cell,可以理解成把多个完全相同的cell合并在一个cell里,如下图所示,集成2bit的multi-bit cell的clock inverter是共享的,那么可以节省2个clock inverter的面积、功耗。同时由于flip-flop数量减少,时钟互联线也减少,即减少了clock net length、capacitance、clock inverter更利于总功耗的降低。

有一点非常重要,MBFF对SBFF的合并使用目的是降低功耗,但是前提是保证timing,若timing不满足,MBFF是应该被要求拆分成SBFF,SBFF更方便resize、move等操作。

有一点非常重要,MBFF对SBFF的合并使用目的是降低功耗,但是前提是保证timing,若timing不满足,MBFF是应该被要求拆分成SBFF,SBFF更方便resize、move等操作。

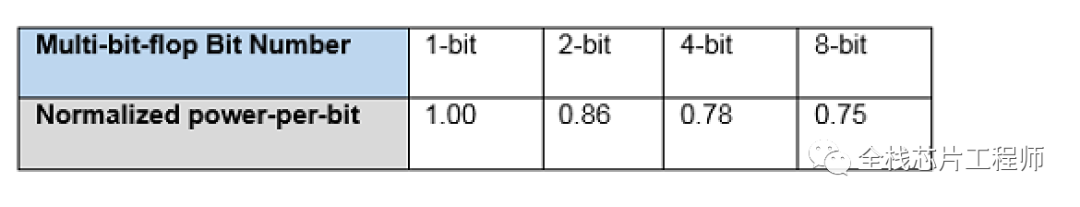

芯片功耗很大一部分在时钟树上,通过multi-bit cell技术我们可以获得如下图所示的功耗改观:

此外,通常scan DFF由于带了scan mux电路,其面积会更大,而Multi-bit flip-flop (MBFF)合并单bit寄存器后,可以更明显降低面积,以scan DFF为例,single bit 和multi bit的逻辑关系一般如下:

在晶体管级别的版图设计过程中,会采用优化晶体管连接,晶体管共用等手段来节约面积,因此multi-bit cell比同等bit数目的single-bit cell的版图面积总和要小一些。假设一个1-bit DFF的面积为  ,那么一个2-bit DFF的面积一般会比

,那么一个2-bit DFF的面积一般会比  小一些,4-bit DFF的面积会比

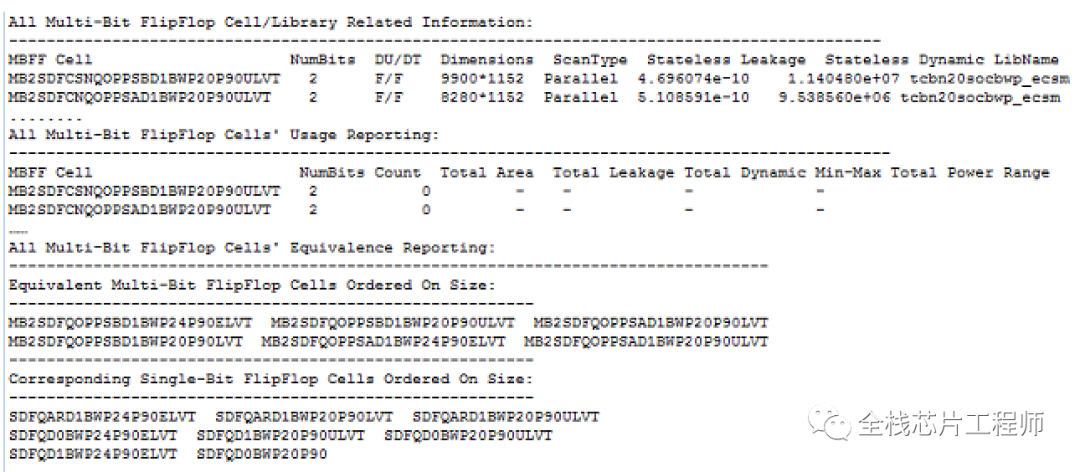

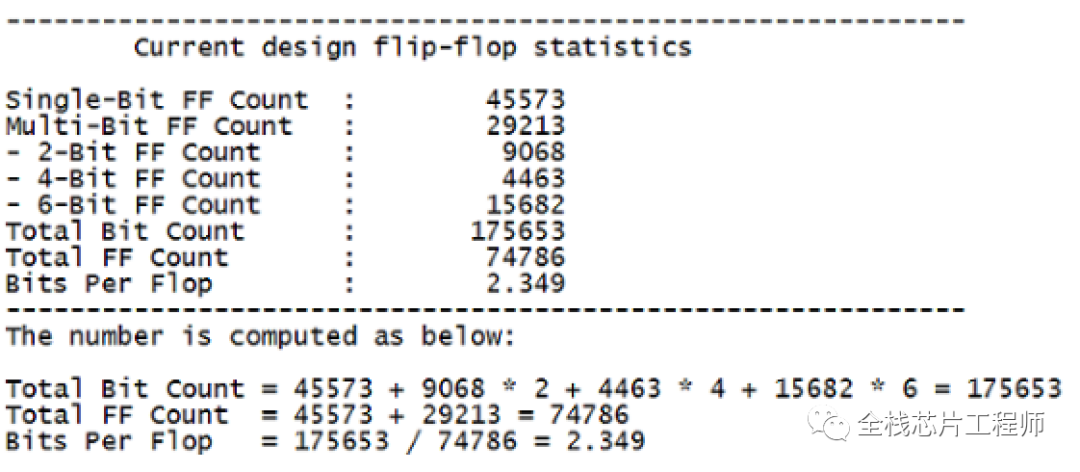

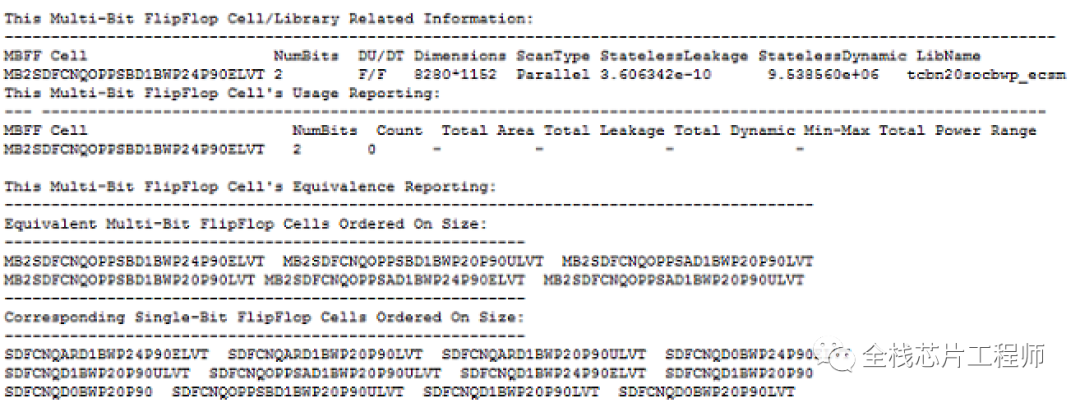

小一些,4-bit DFF的面积会比  小更多。在Cadence INNOVUS中可以用如下命令查看MBFF信息:- reportMultiBitFFs -all

小更多。在Cadence INNOVUS中可以用如下命令查看MBFF信息:- reportMultiBitFFs -all

- reportMultiBitFFs -statistics

- reportMultiBitFFs -statistics

- reportMultiBitFFs -cell MB2SDFCNQOPPSBD1BWP24P90ELVT

MBFF结构在功耗上带来的好处主要体现在以下几个方面,整体而言,就是减少了clock net length、capacitance、clock inverter。

MBFF结构在功耗上带来的好处主要体现在以下几个方面,整体而言,就是减少了clock net length、capacitance、clock inverter。

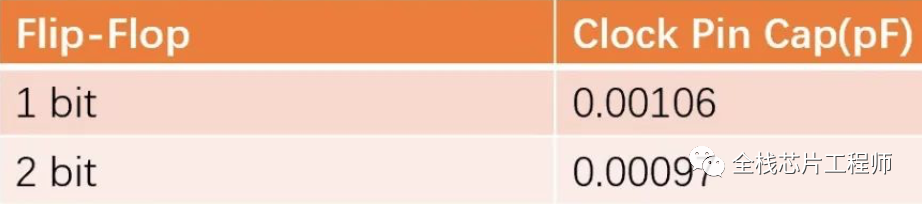

1)clock pin capacitance减少从而降低clock switching power

由下图可知,虽然2bit MBFF较1bit flip-flop的clock pin cap改观不大,但当design中有大量multi-bit DFF来替代single-bit DFF时,DFF数量大量降低,芯片时钟树上整体pin cap的下降是非常明显的。cap越小switching power也越小,动态功耗降低。

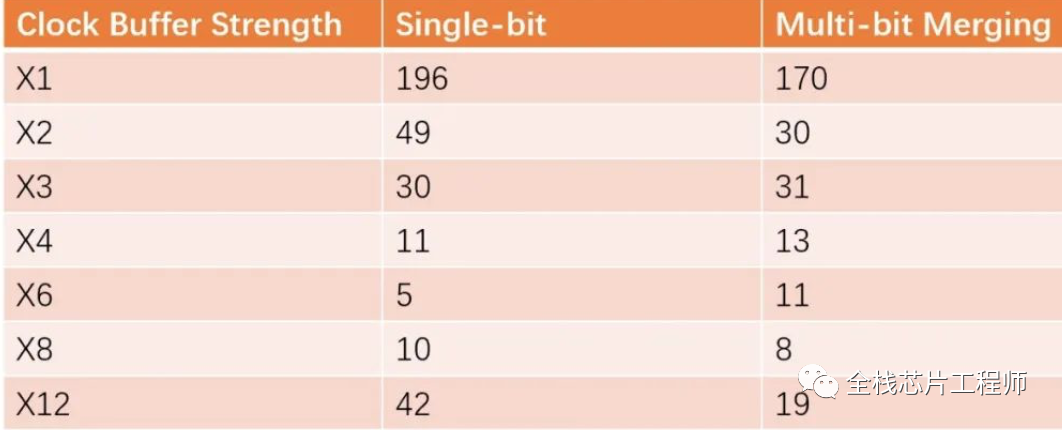

2)时钟树buffer数量减少,降低switching和leakage power

2)时钟树buffer数量减少,降低switching和leakage power

由于multi-bit DFF中每个DFF的clock pin cap相对于single-bit DFF有一些减小,那么在multi-bit design中一个相同的buffer可以驱动更多的MDFF,当然最主要还是DFF数量的减少,从而显著减少时钟树上的buffer数量和面积,进一步降低时钟树上的功耗。 3)时钟树绕线资源减少,时钟树寄生RC从而降低dynamic power

3)时钟树绕线资源减少,时钟树寄生RC从而降低dynamic power

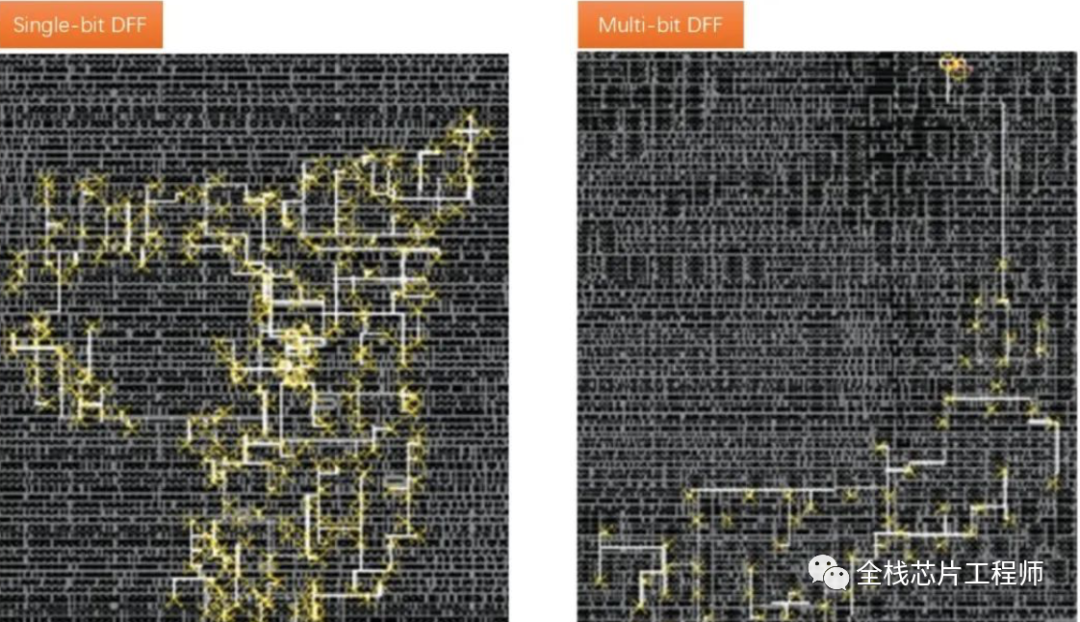

MBFF大量使用时,相对于single-bit design来说,芯片standard cell数量大幅下降,而且在很多时候DFF的摆放也可能会更加集中,时钟树绕线将节省大量走线资源,进而减少整个时钟网络的寄生RC。下图展示了single-bit DFF与multi-bit DFF的绕线差异,可以看出右侧的MBFF绕线明显更少,时钟整体的寄生RC得到减少,从而降低功耗。

尽管multi-bit有以上诸多优点,但是在实际应用中并不总能得到最好的结果。其主要原因在于以下几个方面:a) single-bit到multi-bit的转化有诸多条件限制,很多时候design实际的multi-bit cell比率不高。b) multi-bit cell摆放不合理可能会引起congestion问题、timing问题,反而会增加更多的组合逻辑的power从而抵消clock tree上带来的功耗降低的效果。比如,2bit single-bit DFF本来被place在不同位置,若合同为2bit的multi-bit DFF后,routing连线可能反而更长,增加了路径延迟,工具会采用buffering、sizing的优化方式优化时序,若依然不能满足timing,那么multi-bit cell不如拆分成single-bit cell,因为single-bit cell可以更方便resize、move。c) IR/EM方面的考虑可能会故意让multi-bit cell互相摆放的远一些,从而无法达到减少clock net length寄生RC从而降低功耗的效果。

转载:全栈芯片工程师

- 分享

- 举报

暂无数据

暂无数据-

浏览量:8623次2022-01-11 09:00:13

-

浏览量:8194次2021-12-21 09:00:31

-

浏览量:5502次2022-08-17 09:01:18

-

浏览量:8425次2022-04-01 09:00:15

-

浏览量:4105次2022-03-01 09:00:10

-

浏览量:4884次2022-02-22 09:00:14

-

浏览量:2262次2019-10-30 15:52:40

-

浏览量:3217次2023-11-22 11:57:38

-

浏览量:6597次2021-08-05 17:00:59

-

浏览量:4939次2021-03-15 16:40:15

-

浏览量:5412次2021-04-01 16:44:16

-

浏览量:2276次2020-07-04 09:54:06

-

浏览量:3535次2022-02-20 09:00:19

-

浏览量:2642次2020-10-19 18:05:06

-

浏览量:2411次2020-06-30 18:42:30

-

浏览量:2873次2020-07-15 18:42:34

-

浏览量:1740次2019-09-16 14:08:20

-

浏览量:3098次2019-10-22 14:46:47

-

浏览量:2439次2020-06-13 10:18:59

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友